用verilog A 在spectre下仿真 无结果

时间:10-02

整理:3721RD

点击:

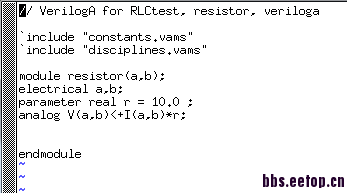

自己用verilogA写了一个电阻,代码如下

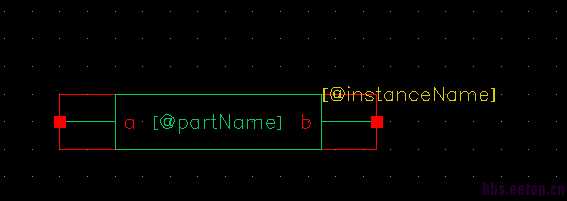

然后根据提示建了symbol(此symbol自动生成,直接保存了,没有任何别的改动),如图

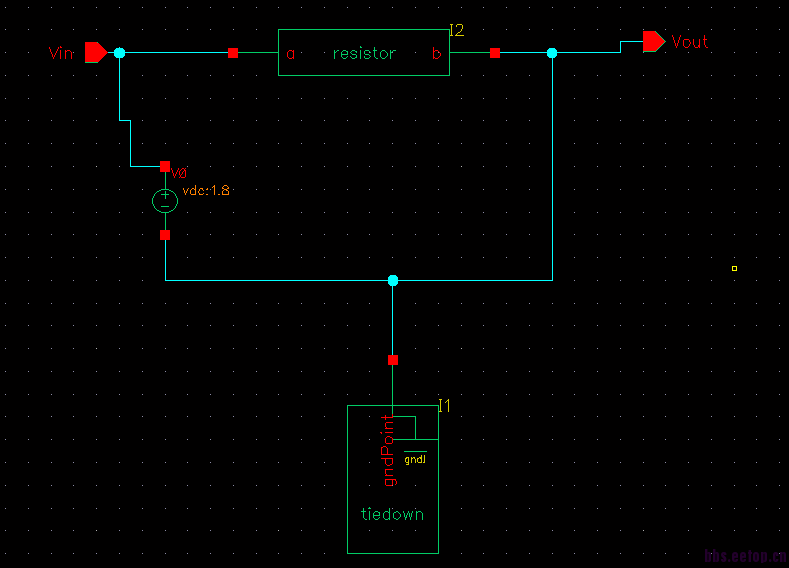

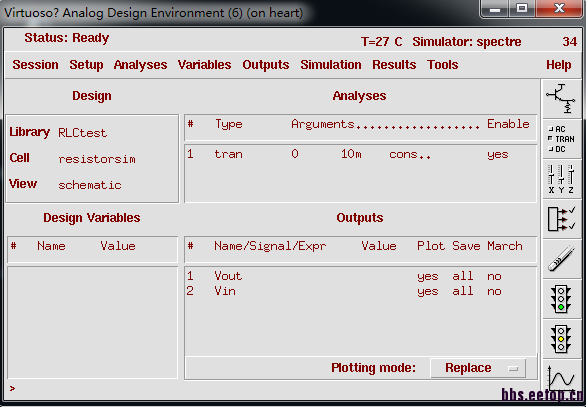

然后建了新的cell,仿真这个电阻,电路和仿真环境如下

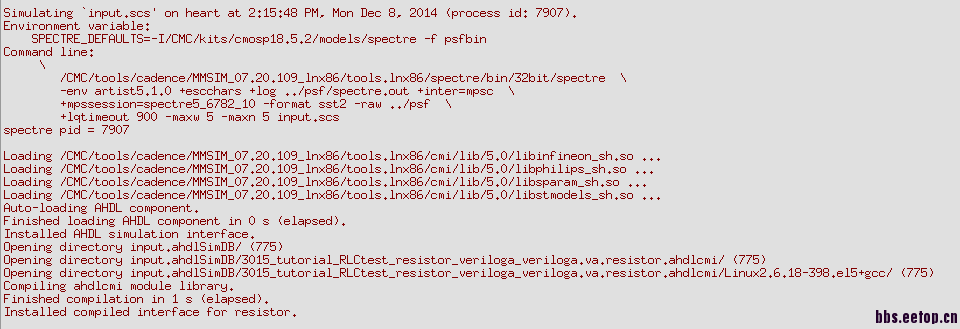

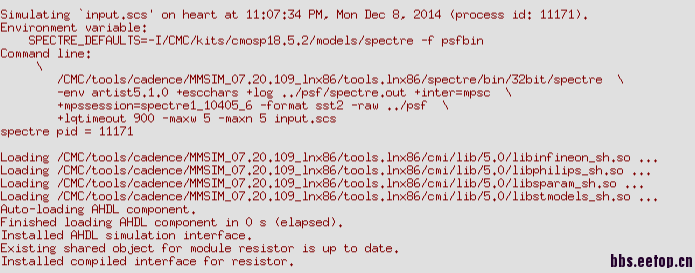

但是无法出仿真波形,下图为系统提示

之前我用内置的电阻代替了我自己写的verilogA的电阻进行了仿真,可以得出正确结果,所以比较怀疑是code的问题。

本人Cadence菜鸟,求教各位大神指点!感激不尽!

code在最下面的图片上!

你加电流源应该就没问题。你应该把电流等于电压的什么关系再写一下,否则,它只认电流,并且你要限流,电流不能达到无穷大

http://www.designers-guide.org/VerilogAMS/basic-models/resistor/resistor.va

你看看这个论坛上建的模型,不过跟你也差不多,可能是我说错了,你试试吧!

漏掉了端口是输入还是输出

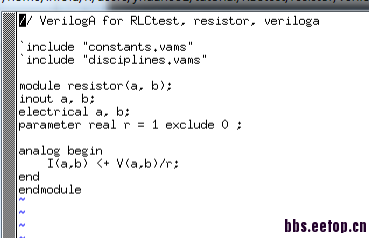

我现在把code根据改成这样了(我是根据一个内置的resistor的代码改的 ) 还是一样的结果

没看出来和ahdlLib里有什么不一样,你的地看起来很奇怪

看我给你的那个连接!

这个ground是根据一个tutorial来的,反正这个电路接一个正常的cmosp18里的resistor,是完全可以正常仿真出结果的 应该就是程序不对

之前没注意看,你的这个测试平台很奇怪,你想测试啥?下面挂的什么东西?代码能贴出来不?一般都只直接用analogLib下的gnd做地,不知道你这个是啥东西!

电路图没变

但是仿真如下,真是抓狂啊!

另外 我想问一下, 每次我编辑完或者修改完verilogA的code后,需要在对应创建的symbol里做什么修改么?

我之前根据一个tutorial里的两个例子(RLC 和inverter)测试过Cadence里的spectre,里面就是用的tiedown接地的

我现在目的是自己用verilogA创建一个模块,然后仿真测试,我想先写一个电阻试一下软件的功能。但是这个code写出来的电阻不能仿真,同样的电路我换成cmosp18里的内置电阻,就可以正常仿真。

不胜感激!

你先用 ahdlLib 里的 res 试一下,看看是不是你的test bench有问题 一步步排除

那就不清楚了!