关于一个EEPROM cell的工作原理

时间:10-02

整理:3721RD

点击:

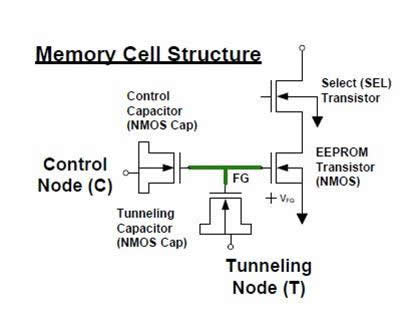

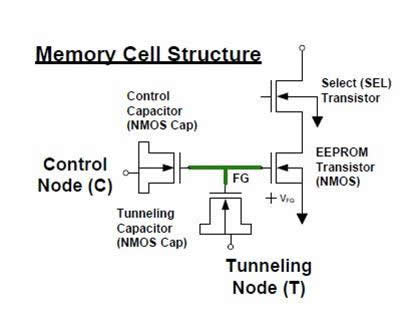

如图所示,最近看到一个EEPROM的存储单元,但一直不太明白为什么用两个MOS cap接到存储管上,如何实现写和擦功能的,请大侠指教!不胜感激!

画的真难看。既不是示意图也不是结构图。而且还有相当的misleading。

你说我时态没有和少东西,你帮我看看,我没发现啊

能否讲讲misleading在哪里?另外如果把那两个mos cap换成电容的符号,是不是就能代表这个cell的模型了?

eeprom mos上有两个栅,一个浮栅,一个控制栅,控制栅和sub会形成一个mos电容,浮栅在靠近有源区的其中一侧有个微小的区域里栅氧更薄,所以形成一个图上所示的tunnel mos cap。这个图是想表达的这两个电容,但是画成这样会让不了解的人以为是三个mosfet构成一个eeprom。

control node 是要接电位的,tunnel node事实上就是mos的S/D。在没有eeprom工艺支持甚至只有1层Poly的情况下,这样弄也是可以的。但是foundry不会帮你保证yield

其实single poly e2就是这样的

你说的没错,1P的E2就是这样,但是我觉得1P来做E2只能是很无奈的做法,这个时候对E2的能力要求不能太高了。

我觉得LZ的原理图的样子,LZ十有八九就是只有那么几个bit的E2,工艺应该就是1P E2的工艺了

大概1Kbit 的样子。

learning !

以前道是没有主义

请教一下eeprom擦写的控制电压是怎么产生