隧穿效应仿真问题(普通CMOS管做EEPROM)

时间:10-02

整理:3721RD

点击:

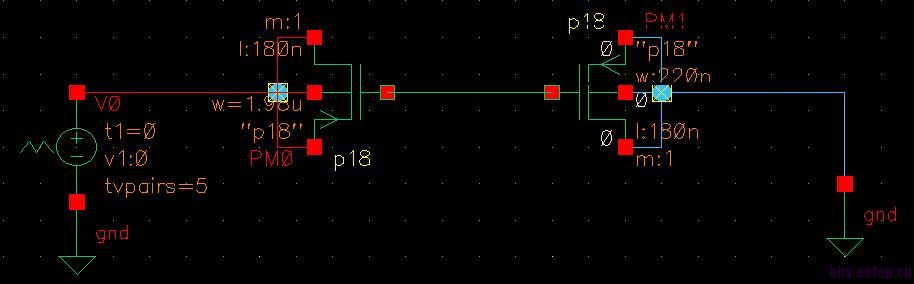

电路图如下所示,两个管子是SMIC18工艺中普通的PMOS管,直接从库中调用的,左侧管子W/L=9,右侧管子W/L=1,使左侧管子与右侧管子的面积比约为9:1

此时若在左侧电压源加10V电压,根据电容分压原理两个管子栅极应该是9V,则会发生隧穿效应;断电后电子会保持在栅极上。

我的仿真结果如下图所示,第一个波形为电压源,第二个为栅极电压:

问题1:栅极电子保持时间为什么只有几毫秒?这样完全达不到EEPROM保持数据的要求。

问题2:若在电压源加一个较低的电压(理论上不足以发生隧穿效应),但在栅极上依旧有电压下降的现象。

期待有相关经验的大神指点!

spice仿真器仿不出来的

谢谢你的回答。

你是说spice仿真器不能仿真隧穿效应是吧? 我了解到eeprom工艺仿真是用一个等效模型,那普通的CMOS工艺是怎么仿真的?

eeprom 和標準 LOGIC CMOS 同一類嗎?

eeprom一般是2p?m的工艺,但是用两个1p?m的管子也可以,就是不知道怎么仿真。

保持不了,那肯定有漏电。

workable?