带隙出现过冲

时间:10-02

整理:3721RD

点击:

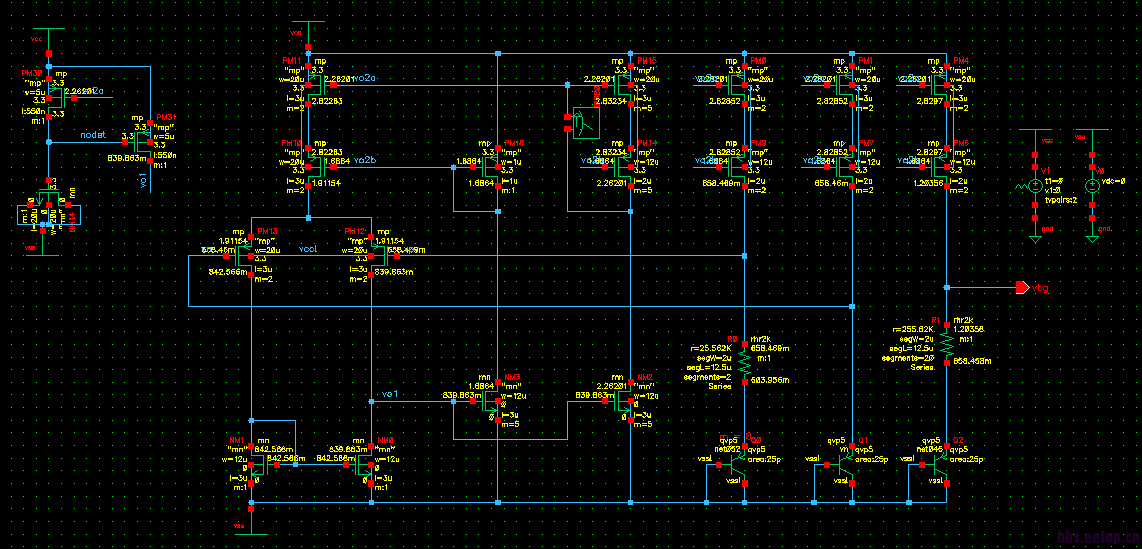

带隙出现过冲什么原因

我这样防环路稳定性 对吗

环路稳定,相位裕度60怎么还过冲

BG的过冲也有可能是start-up造成的

图呢?。

有啊

上电过冲的仿真图

加个电容?

这都是4级系统了,出现什么都可能。带隙用4级系统,有点过量了吧。

相位裕度是60度的反馈系统的阶跃响应本身就是有过冲的。没有过冲那是90度的相位裕度。

电路本身没什么问题。

iprobe加的位置不对,应该在vo1的地方插入,仿真的PM才是对的。

在vo1和gnd直接加cap作为补偿,串联一个电阻会更好一些。

voo1应该链接Source或电源,图中看起来像是悬空

谢谢,iprobe位置确实不对

谢谢小编