请教cmos管子宽度意义

时间:10-02

整理:3721RD

点击:

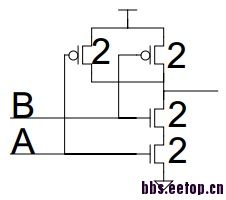

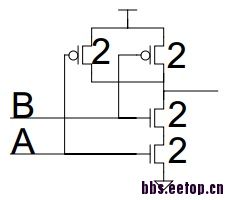

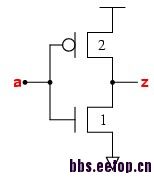

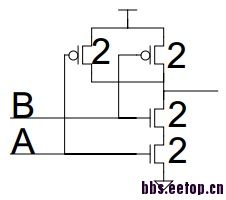

记得看书的时候,讲到gate sizing的时候需要匹配最差情况下pull-up和pull-down的电阻,如下图,

,

,

但是在真正设计电路的时候(比如在cadence或Hspice中),pmos和nmos的尺寸却不是按照这个尺寸比例,比如用spice模拟时如果宽度选择一样的话输入和输出延迟差异很大,但按大概2:1的比例则输入输出很接近,请问这两种宽度的关系是什么?这里有些晕,请教各位,

谢谢,

,

,但是在真正设计电路的时候(比如在cadence或Hspice中),pmos和nmos的尺寸却不是按照这个尺寸比例,比如用spice模拟时如果宽度选择一样的话输入和输出延迟差异很大,但按大概2:1的比例则输入输出很接近,请问这两种宽度的关系是什么?这里有些晕,请教各位,

谢谢,

这种问题,自己看书就能找到答案,怕是微电子专业的大学生的基本常识吧

nmos和pmos的多子类型不一样一个是电子,一个是空穴,他们的迁移率不一样,即电流计算公式中的u,一般工艺差不多2:1的关系(我确定不是这个值,不过约等于)所以,pmos的尺寸大一点(约取nmos的两倍)。

就是空穴和电子的迁移率的比例接近1:2

十分感谢各位,

书上感觉说的不是很细,有些点没有串起来,总觉得比较零散,在下用spectre模拟的时候inverter确实是按照pmos和nmos宽度比例2:1左右(180nm工艺,pmos 900nm nmos 400nm左右时),和下图1相符;而nand2(同一个工艺下模拟,pmos为800nm nmos为400nm左右)却宽度比仍旧为2:1左右,和下图2不符。不知在下是否把管子宽度的问题搞混了,或者说所有设计都需按照2:1的比例进行,然后再微调,不需要匹配pull-up/pull-down么?测试标准是输入延迟和输出延迟差异越小越好,按上述尺寸跑仿真的结果是非常接近的,也即都是2:1左右结果最好,nand2调整pmos和nmos相等的情况下差异却非常大,

在下本科不是这个专业的,的确比较晕,可否推荐本您认为讲的比较清楚的参考书?谢谢,