求教一下流水线ADC的采样电路问题

时间:10-02

整理:3721RD

点击:

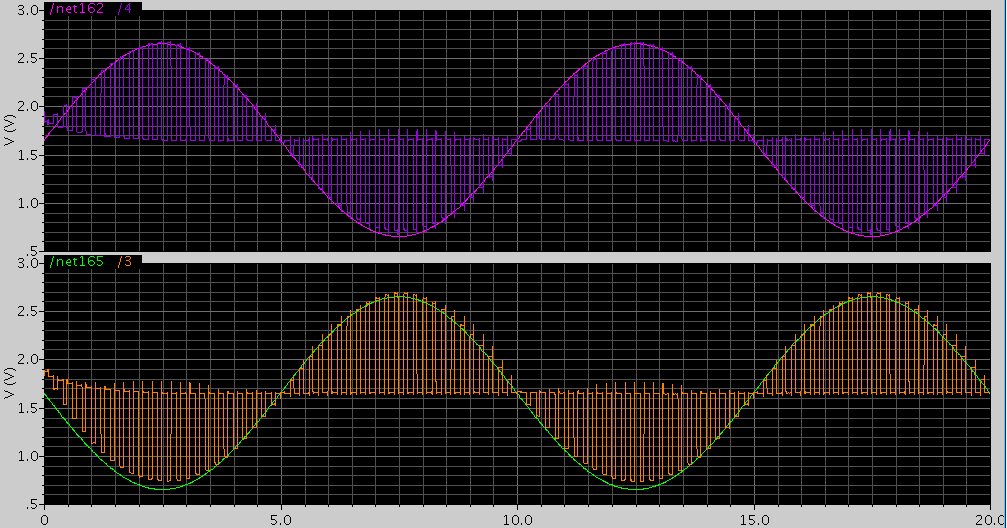

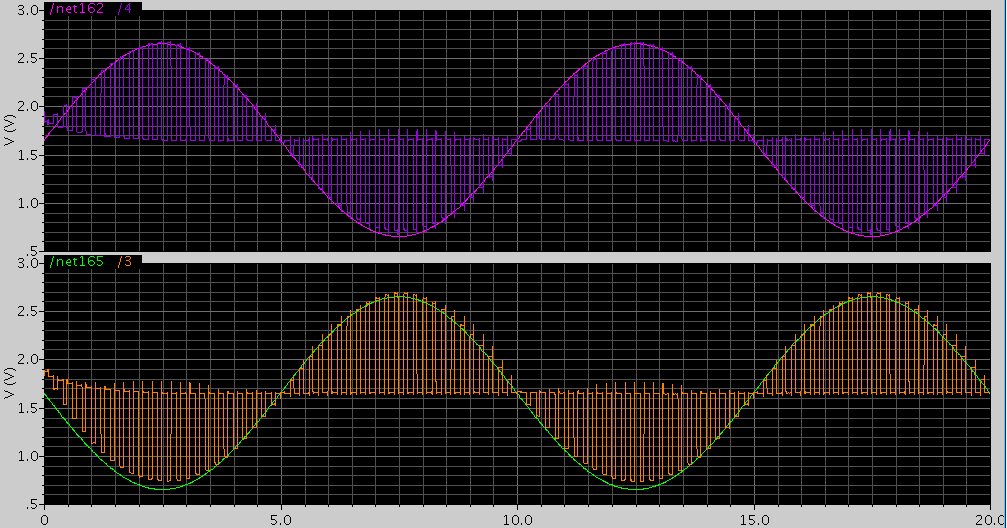

我正在做流水线ADC的前端设计,做完采样保持电路后的仿真达不到效果,不知哪里出现问题,还望各位大侠帮忙看一下,下图是双端的分别输出,采样点和输入波形偏离最大有0.1v。

这个应该是运放没做好,原因可能是你运放的输出摆幅不够,同时输出电压的变化对运放的增益可能也有很大的影响,从而产生失真。

首先输出波形的上下摆幅不对称,存在幅度被挤压的情形,这个应该是你运放输出摆幅不大够,建议你测试一下运放的输出摆幅是否满足你的要求。

其次,你两个输出端的波形也不大对称,这个可能是你运放的工作点设置得不是很合适,从而导致了正负输入端小信号经过的时候对各个管子的工作点影响比较大,并且不对称,所以才会产生这样的波形。建议你可以仅对运放跑个闭环瞬态特性,看看它输入端的波形是否对称。通常来讲,如果运放设计的好,它输入端的波形应该是会出现很规律对称特性。

另外一个就是你为什么不用乃奎斯特采样率?如果那样的话你可以通过MATLB程序来计算输出端信号的信噪比,这样就可以更加量化。因为运放的有限增益,输出端信号的幅度确实会在幅度上比输入信号的幅度要低一些,但是这个差值在各个采样点变化应该不会很大。所以有时候观察到的也不一定准确,还是通过计算SNDR会更为直接。

不过可以肯定的是,你这种情况应该是失真造成的,另外你还可以关注下小信号建立时间,看是否满足要求。

这只是我个人觉得如此哈。

从图形上看,没什么大问题

只是outpout common mode voltage有点漂移

没有太大关系

输出看一下differential output vs differential input就可以了

如果这样也有大的误差,那么就是你的output range不够,在检查一下opamp

多谢各位指点,我再检查一下

多谢指点

CMFB ?!