不知道该怎样给一个ADC定设计指标

SNDR(ENOB),NL,throughput,POWER CONSUMPTION,AREA,最主要的就这几项了

还在做pipeline的ADC啊,14bit,200M都出来了。再高就难做了,低了又没意思。

楼上是牛人啊,14bit,200M都出来了(ADI,TI确实是出来了),只是不知道实际流片出来的ENOB有多少?国内哪家公司做出来可以去拿核高基专项资金了,先不说ADC本身性能如何,测试仪器恐怕国内就无解了。高精度高速信号源,高精度时钟源,高速逻辑分析仪……或者你采用DA-AD法来测试还是用别人的评估板替换测试?反正我是不太相信国内有人能做。

DAC和ADC没意思,都给大公司做烂了,小公司做不好,毕业设计做这个真心不好,没有任何意义

牛人,牛人。国内貌似就某校写了个14BIT 200MSPS的PAPER,做到11位不到。

做烂?你也不数数一共有几个公司有产品

說的容易.....

實際上做出來有幾人?

学习学习

拿核高基的几家应该都有吧

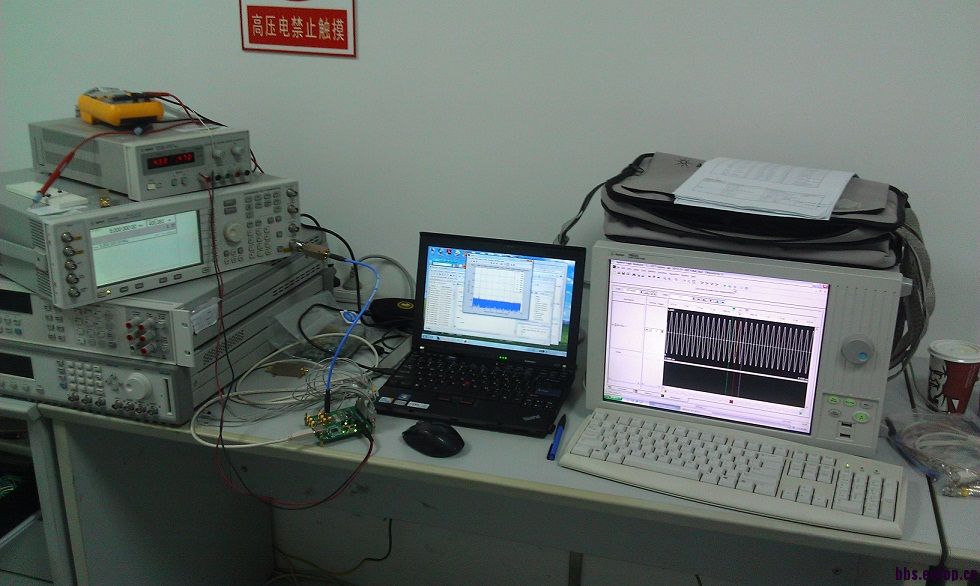

测试简单,自己做块板子,找个安捷伦的信号发生器,逻辑分析仪,在找几个minicircuit的带通滤波器就可以测了,要不要我给你看看我的testbench

国内貌似14位250M都出来了,250M下enob 10.8,不过良率不行

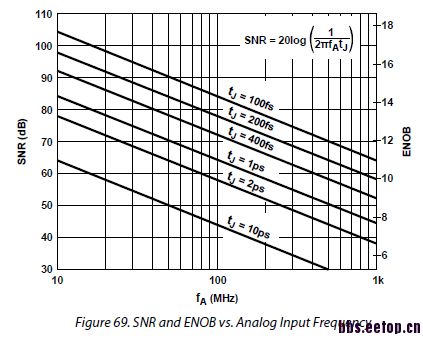

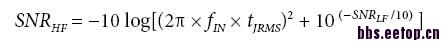

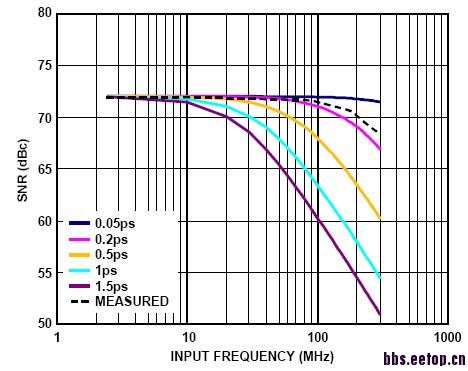

一段时间不来,EETOP上牛人辈出啊,原来14位,200MSPS的ADC测试如此简单,自己做块板子,请问老兄准备做几层板,噪声串扰电磁辐射等问题如何解决?找个安捷伦的信号发生器,逻辑分析仪,说得真轻巧,请你推荐一下相应仪器呢?16位100M的信号源有吗?N33522?逻辑分析仪N16820够吗?要满足14位,200MSPS的测试要求,时钟发生器的jitter要小到什么程度你想过吗?不要测过一个十位,几十兆的ADC就开始认为测试简单,这样只会显得自己浅薄。

ENOB只有11 位不到,也好意思说自己是14位的?250MSPS的throughput是设计难点吗?关键的是你的输入信号频率FIN是多少?先不按最苛刻的NYQUIST计算,就算通用的标准1/3的采样频率算,如果对80M的输入信号采样,能获得11位的ENOB,我觉得这个水平在国内都不错了。如果只考虑设计指标,不管实际流片性能,那别说14位,200M,就算16位300M又有何难?流片出来,用这个所谓的16位ADC配合几百兆的时钟去测一个几十K的输入信号,获取一个11,12位的输出,再大言不惭地说自己做了一个16位几百兆的ADC?

对你的testbench感兴趣,拿出来showshow?

signal generator: Agilent4432/4438/8663------> signal & clock sorcue

logic analyzer: Agilent 16800 series

badnpass filter: minicircuit 1MHz/5MHz/10MHz/20MHz/40MHz/100MHz....

然后再加一个电源即可

你觉得bottleneck是什么?

呵呵,agilent16820怎么就不能测14bit/200M 的ADC了?16800系列每个port 16bit,有2个或4个port,最高可支持到500M到1G,以前我们DDR测试都是用16800

关于PCB,你觉得PCB层数越多越好么?测个ADC做4层或6层就够了,不就是一对dirrerential pair,底下给个完整的ground plane,其实ADI或TI的demo板都做的很烂,都是实习生画的

E4438或者8663的phase noise足够低了,再做bandpass filter,SNR测个70多不到80dB还是没有问题

信号源用lc滤波,产生16bit很难吗?14位200mps的logical analyzer是个问题?还串扰和电磁辐射,这些不都是基本功?clock jitter当然要小,这部分可能是最难的,不过既然是测试,power和pin都不是问题的话,也不是不好解决,当然low jitter clock是另外的问题,这里测adc.

14bit 做出来才10.8bit 还是不要拿出现眼的好,因为这个resolution 的后2位可有可无,你就当它是12位就好了

要我说,高速而且是欠采样的情况下还讲什么有效位

在nyquist 的时候enob 多少呢?

还真不能这么说。比如在基站应用中,155MSPS左右的SAMPLE RATE,但是IF可能会放在第二或者第三NYQUIST区。而其典型的指标要求就是80dBc左右的SFDR,70dB左右的SNR。其实PIPELINE的一个主要应用就是欠采样。我个的经验来看,高IF时的高线性度和低噪声,比高的SAMPLE RATE还要难

我觉得可以再思考下以下几个方面

1. 信号前端的配置,当测试的IF频率不同,前端的电阻电容也需要调整,所以先需要了解ADC自身的S参数

2. 时钟源的相噪。你可以测测8663的相噪,测测就明白了,-160dBc左右的相噪。那么高IF时,70-80dB的SNR是不是有点扯了U

3. 我个人真不喜欢用罗分。一个是采样深度太小,静态测试很难用。最主要的是,测试的实时性的问题,尤其是在debug的时候,你调一个设置,或者改变一个信号幅度,信号频率,你就得去采一次数据,点一次MATLAB,确实没效率。

其实,测试方案好不好,买一颗ADI/LTC的芯片装上测测就知道了,看离DATASHEET有多少差距。我个人的经历来看,这个东西要测出个function不难,但是要测出好的性能,真是够专研的

板上做阻抗匹配那是必须的,当然对于不同频率的信号,会采用不同的transformer连接

至于你说的8663,我当然知道它的phasenoise和jitter,所以测个100MHz左右的信号,到70dB+的noise是没有问题

我也知道Wenzel 的OCXO是个好东西,NASA用的东西能不好用么?但是像我们这种屌丝用不起啊

至于测试平台,我当然知道最好弄个数据采集卡,最好还有ADI或TI的GUI,一键自动run起来,那当然爽了,可是咱没那么好的条件,只能苦逼的手工抓data

不过就ADC 来说,debug还是真不算不太复杂,而且也就为一个project,没多少budget,所以凑合一下就拉倒了

追求极致是没有底的,只要够用就好,不仅设计要tradeoff,测试也要tradeoff

呵呵,那可能是我们体会不同吧,ADC的debug太难了。不过啥事只要是能凑合,那自然是没必要再深究了。

fuyibin的帖子很好啊,敲了这么多字,比如讲snr和输入频率,时钟jitter的关系的时候又有贴了jitter vs SNR的图佐证。把自己测试的仪器图片贴上来,这些对新手有帮助,对熟练工都有借鉴。

要不你也贴一个你的测试方案

呵呵,几天没来,这个帖子讨论又多了,我的看法和你是一样的,ADC测个功能是很简单,但要真正测到高的性能,测试的难度绝不亚于设计。如果说靠这么几台常用的仪器,就能对100M的信号测出14位的精度,不管你们信不信,反正我是不信。

16bit的信号源不难,但送入ADC的信号高达百兆级别的时候还保证16bit很简单吗?你说得没错,这些都是基本功,但这些基本功又有几个人做好了?最后还对你的逻辑有点不明白,又说jitter很重要,又说是测试ADC,low jitter clock是另外的问题?测如此高速ADC不考虑apecture jitter影响了?

.我不清楚如何为ADC提供精度达到200fs的时钟源,所以要是EETOP的牛人们能提供一份自己平台测试得到的最终性能数据(14位200MSPS,NYQUIST sampling 情况),一定让我大开眼界并从中受益了。

.我不清楚如何为ADC提供精度达到200fs的时钟源,所以要是EETOP的牛人们能提供一份自己平台测试得到的最终性能数据(14位200MSPS,NYQUIST sampling 情况),一定让我大开眼界并从中受益了。

你有没测过高速adc (> 12b的)?楼上牛人贴的方案唯一缺的就是一个好的时钟,许多做这种adc的都会做一个LC PLL 做时钟。要不系统也没法用

请教,差分信号是信号发生器前面板的RF口给的么?我一直用的背后的IQ输出,不知有啥影响不?