13bit pipeline ADC只有50dB,请问如何提高?

在1MHz和10MHz采样时钟下,正弦输入和梯度输入的数字输出功能都正常,

SHA的SFDR是120dB,但是整个13bit的ADC的SFDR只有50dB(1MHz CLK下),请问可能是哪里出了问题?

VREF参考电平,在1个clk内波动0.1mV左右,VREF+和VREF-是对称波动,请问这个会不会对SFDR有影响?

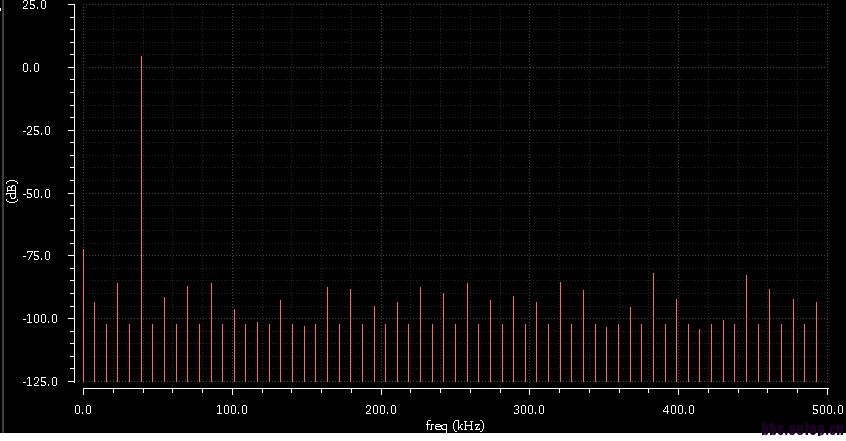

SFDR仿真是用1MHz*3/64的差分正弦输入,1MHz时钟采样64个点,然后dft作图

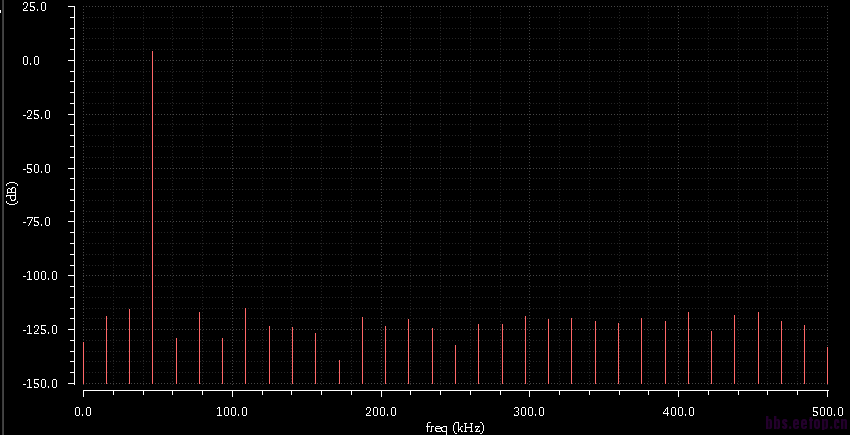

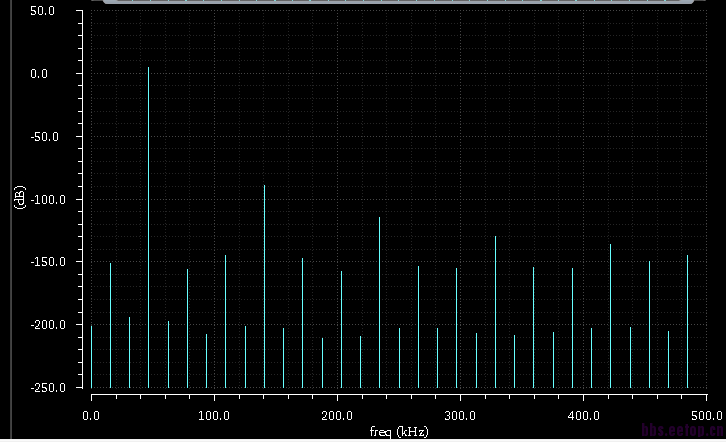

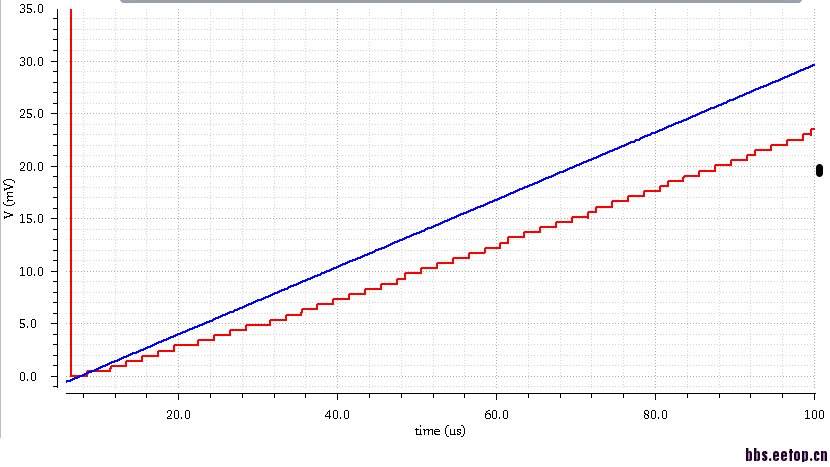

SHA的SFDR仿真结果如下图

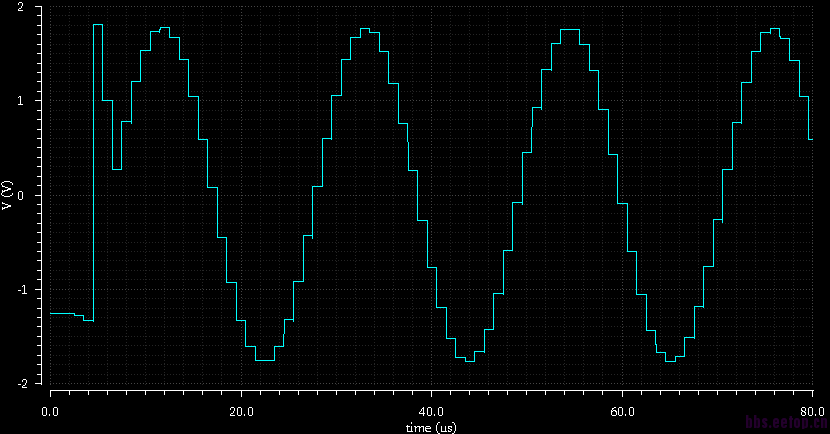

13bit ADC对正弦输入的输出结果如下图(14bit 理想DAC差分转换后)

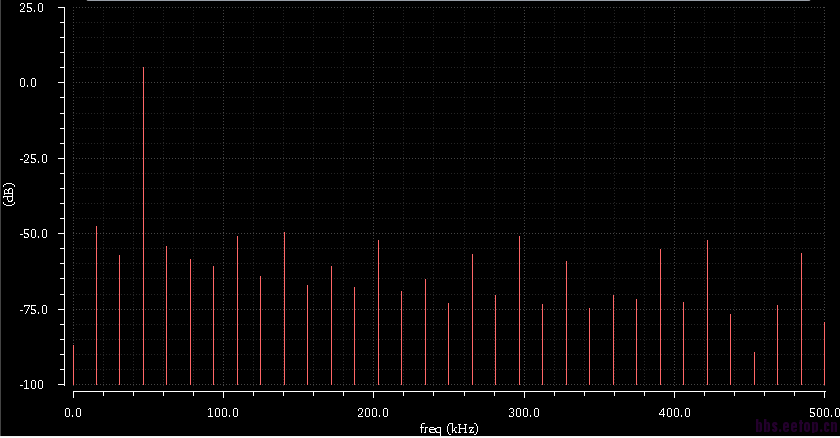

对上图做DFT,得到13bit ADC的SFDR如下图,只有50dB

你这是仿真结果还是测试结果?

如果你怀疑Vref带来的影响,你可以在仿真中使用理想源替代然后观察结果。

想问一下你目前结构中vref会不会输出到pin端?

是仿真结果,VREF会外接的,通过带隙基准和单增益跟随器生成电压,然后外接1uF电容稳定用。这样做合理吗?

仿真时发现,VREF+生成电路可以到3.5V,但是接到ADC上后,就只有1.7V然后花很长时间慢慢上升,于是我在仿真时通过initial node setting 把VREF+强制设定在3.5V,另外两个对电平敏感的参考电平也一样的方法处理。

你的信号路径上的开关的SFDR是多少?

貌似你的Vref驱动能力很弱啊?你要检查一下。

建议还是用理想源替换先仿一下,看看影响有多大。

谢谢,我想可能是因为我加了1uF的负载电容,所以带宽很小,大概只有几个Hz。

按照您的建议,换成了理想的直流偏置参考电压,做了仿真,还是只有50dB。

请问,有没有可能是开关的沟道电荷注入效应引起的?

Vin+和Vin-的电平不一样,所以沟道电荷注入效应引起的偏差电压大小不一样,于是会引入杂波

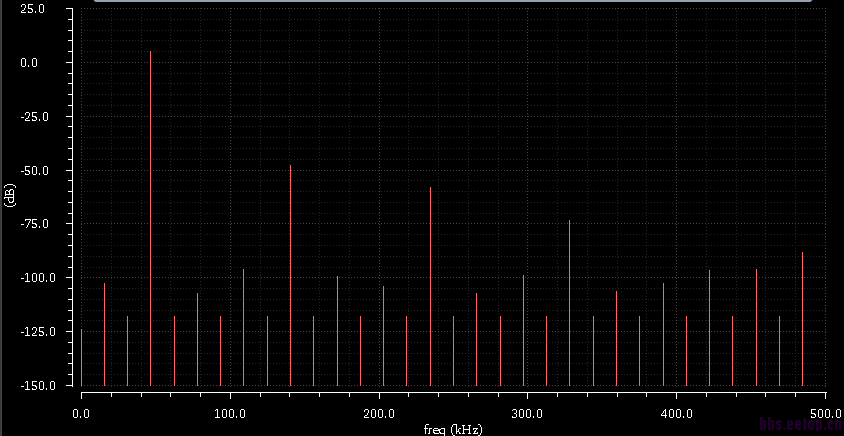

谢谢提醒,我开始的采样开关的尺寸是PMOS: 100u/0.6u和NMOS: 50u/0.6u,仿真开关的SFDR只有50dB,把尺寸改为了PMOS: 4u/0.6u和NMOS: 2u/0.6u,开关的SFDR提高到了90dB,推测是不是因为尺寸增大后,沟道电荷注入效应引起的误差电压增大,SFDR减小。把开关修改后,虽然开关的SFDR提高了,但是13bit ADC的SFDR仍然只有50dB,请问有可能是什么原因?

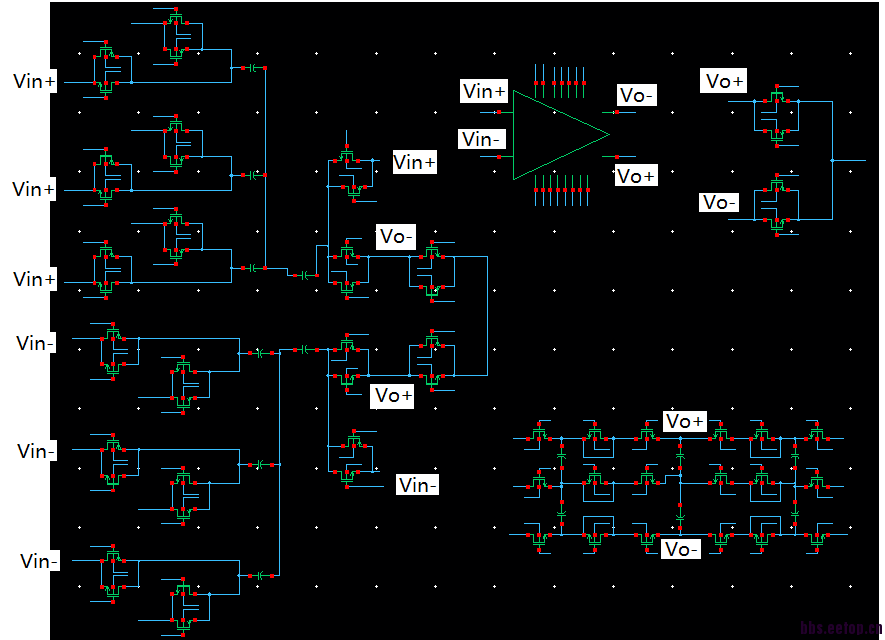

另外第三个图是我的2.5bit 的MDAC的电路图,请问结构有问题吗?

图1 修改前开关的SFDR

图2 修改后开关的SFDR

2.5bit MDAC的结构图

我看了你发的那个13bit ADC的输出转化成的模拟波形,我觉得有问题,台阶太少了,根本不像是13bit的结果。按照那个图的表示能有个50dB的SNDR就已经不错了。你再去确认一下这个转换的过程是否正确。

台阶少会影响SNDR,但是基本不会影响SFDR

谢谢,为提高采样密度减小采样台阶,1024次采样我也试过,SFDR的结果和64次采样相比,没有区别

所以,为了节省仿真时间,我现在用的是64次采样.

请留意小编提供的第三张图,里面不仅仅是谐波差,噪声也差。这就是我想表达的问题。

你好,小编。从电路图上看信号通路上的开关并不是采用的bootstrap类型的开关。你可以搜一下关于bootsrap的开关文献看一下。建议信号路径上的开关先用理想的开关试一下。不管怎样信号路径上的开关是需要bootstrap类型的。

小编你好,你的MDAC的结构好像和一般的结构不太一样。单端四个电容的公共端应该接到运算放大器的输入端。

小编能否把自己的MDAC的原理图画一下。从我的经验来看是原理图的结构有问题。

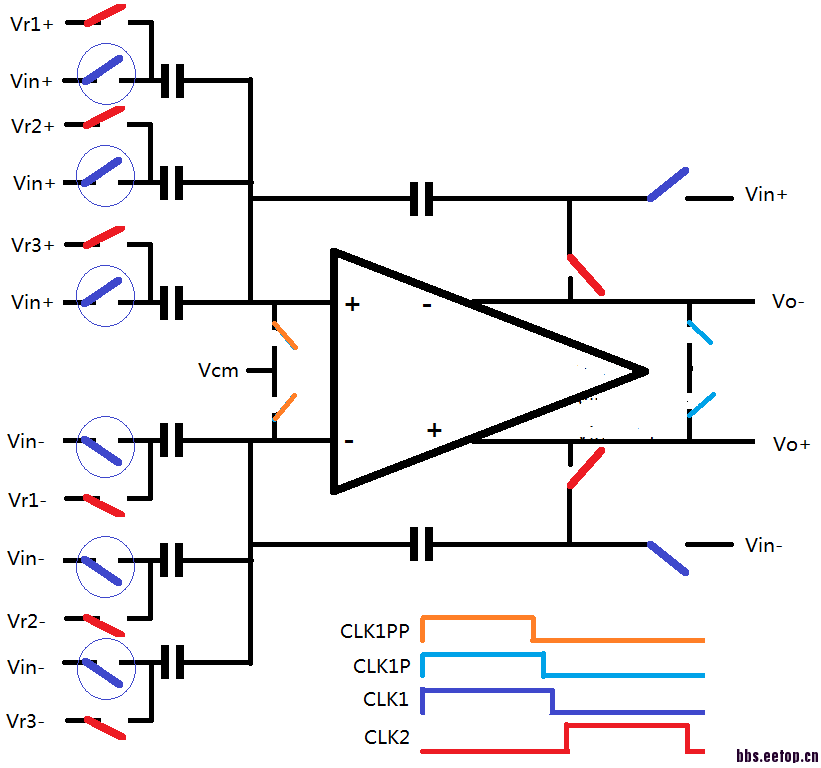

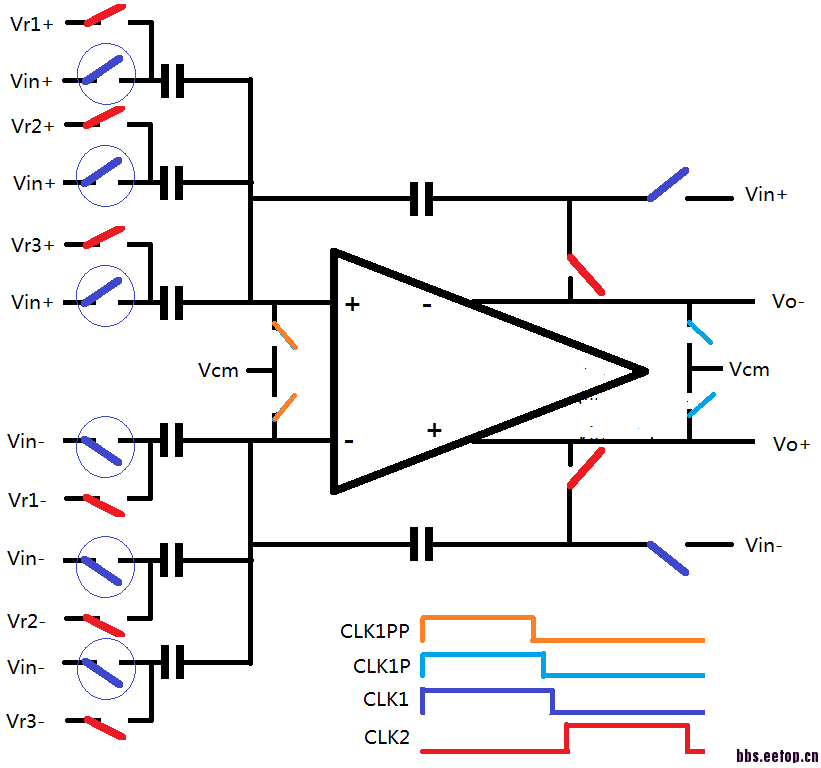

谢谢提醒,我第一次做ADC,在SHA里的信号采样开关用的是bootstrap,MDAC的信号采样开关用的是普通的CMOS开关,我试试您的建议,按下图所示,把所有2.5bit和1.5bit的MDAC的Cs的采样开关换成bootstrap。

我的电路图里,Cs和Cint的底板接的是运放的输入端,我把运放的位置放到旁边去了,连线用的是相同的标名,它们是连到一起的。

谢谢您的建议,我先把MDAC的信号采样开关换成bootstrap开关,仿真仔细检查一下MDAC的结构

luguo,xuexiyixia

我的2.5bit MDAC结构如下图,圆圈的开关是bootstrap结构,红色时钟是CLK2,蓝色是CLK1,黄色和浅蓝色分别是CLK1pp和CLK1p, 我的正弦和斜坡输入信号的仿真结果基本正常,但是SFDR还是只有50dB,请问是我的结构有问题吗?(第一图是正确的,第二个图输出有错误,没有接vcm,删不掉,)

请问噪声差有可能是什么原因?

看了小编的MDAC的结构了。没有问题。

仿真斜坡发现,ADC的输出小于输入信号,如下图所示

我的ADC的bit分配是2+2+1+1+1+1+1+1+1+1+1,其中2.5bit MDAC用的是gainboost op,增益是125dB,带宽85MHz,PM=98度

1.5bit MDAC用的是普通的折叠共源共栅,增益是70dB,带宽100MHz,PM=78度

请问我的1.5bit MDAC的增益够不够用(特别是第三个),是不是因为增益不够导致输出码较小,从而导致SFDR只有50dB?

从斜坡输入不太能确定是否是运放增益过低的原因。可以仿一下第一级2.5B的传输曲线(就是那种分为七段的折线),与理想的传输曲线对比,看看实际的曲线的斜率是否是4。如果是4的话运放的增益和寄生电容的影响就可以排除了。建议尝试一下。

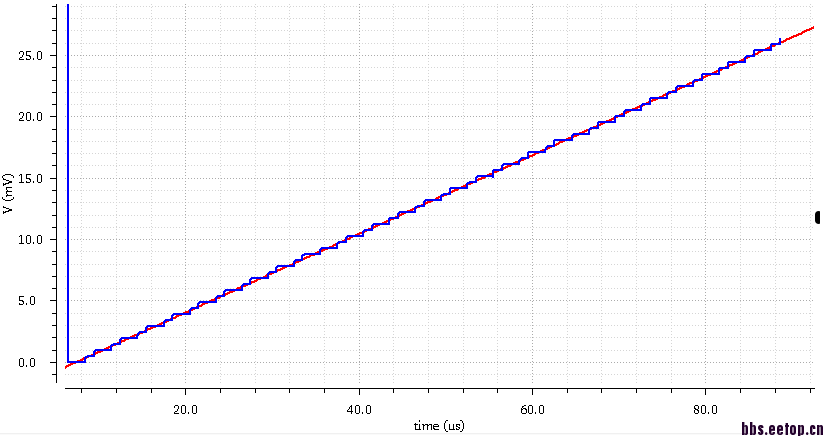

谢谢,确实是2.5bit MDAC没有设计好,修改之后仿真结果正常,输出和输入保持一致,如下图

修改后做了SFDR仿真,CLK选择1MHz,输入信号选择1M*5/128的差分对称正弦,采样128个点,做了DFT之后,如下图,SFDR为75dB,比修改前的64次采样多了15dB,还是偏小,是不是和采样点的数量有关系?

SHA的SFDR有120db,整体75db,建议只将SHA和第一级串联起来,剩下的用11bit理想ADC。仿仿看是多少的SFDR,定位是第几级MDAC 出了问题。13bit的ADC至少要达到80db以上的SFDR。

谢谢,我按照这个方法试一试。

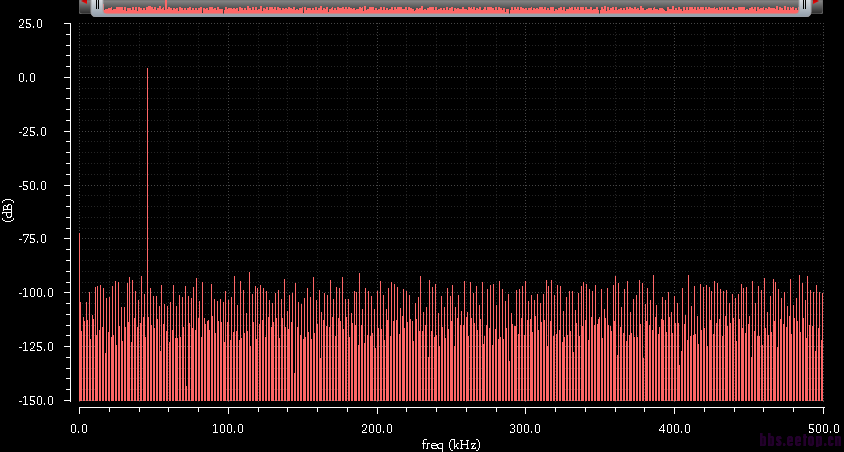

昨天按照1024次采样,仿真得到SFDR结果如下图。在DC 0Hz处有个峰,如果剔除这个峰,那么就有95dB。

看来问题解决了,恭喜

恭喜啊

看每一级的建立时间是否充分,以及仿真时仿真精度maxstep要至少小于1/100时钟周期。