基于CMOS的基准设计的问题望大神解答

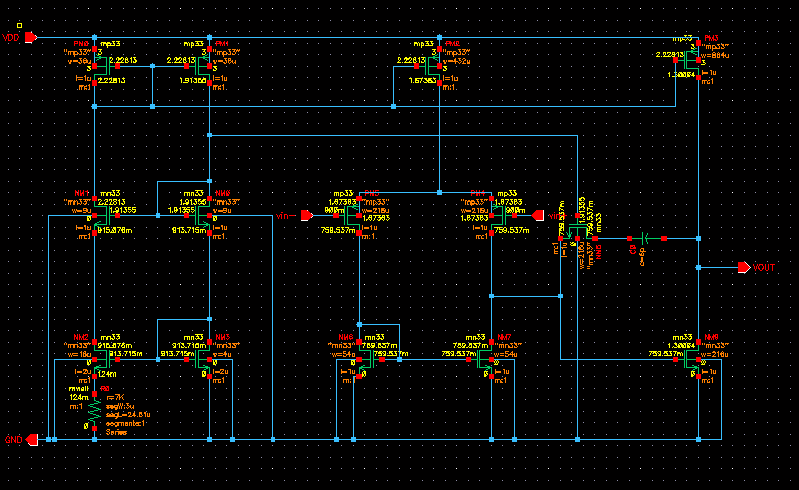

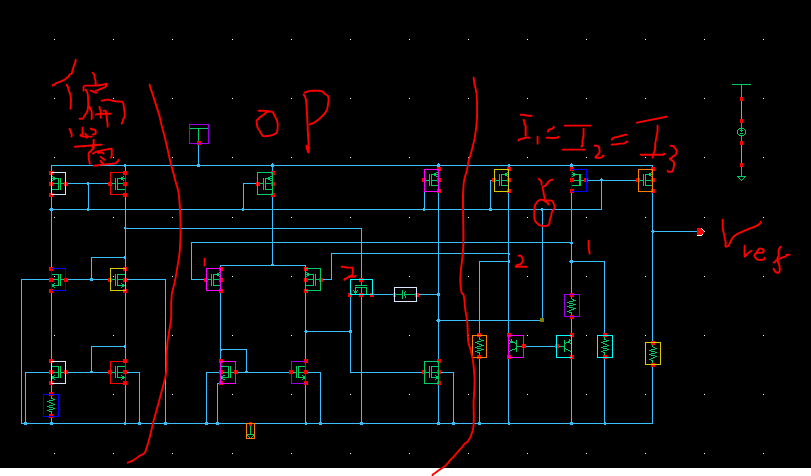

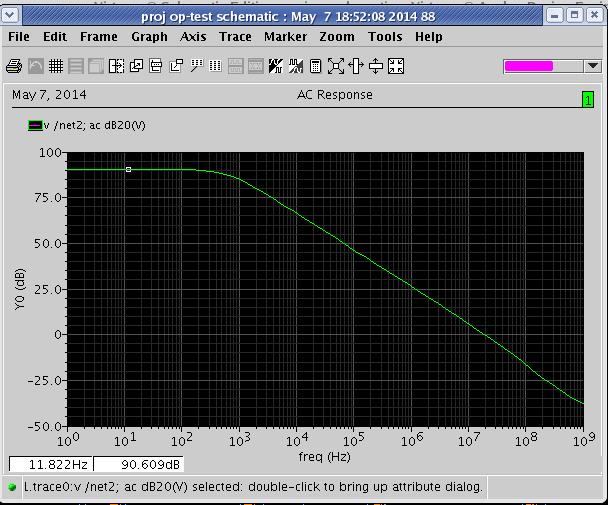

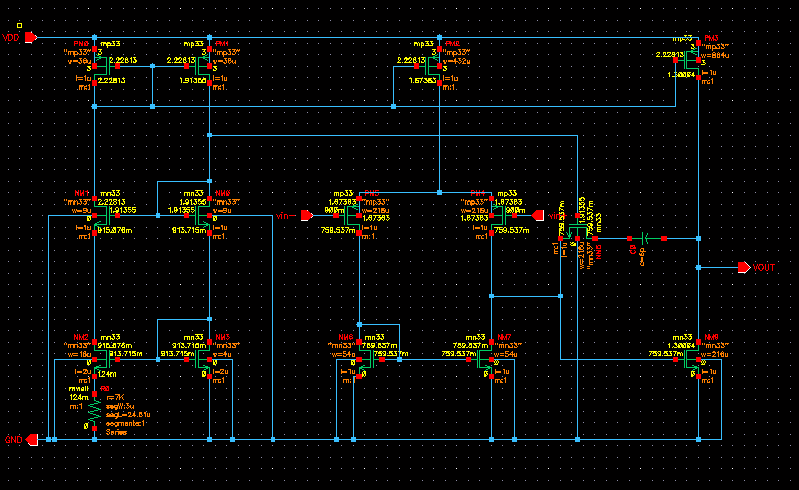

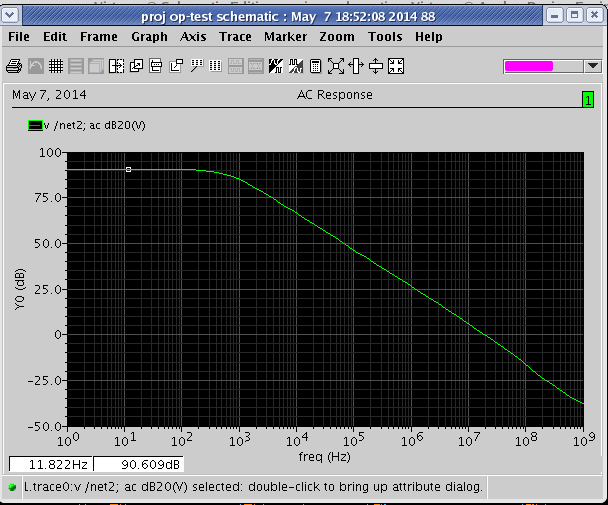

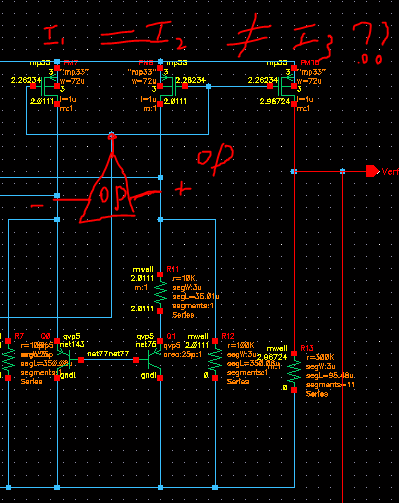

这些是我电路中用到的OP电路,连入基准电路中不知道怎么回事?op电路仿真没问题,图中Y点的点电位

(Y点的电压是由放大器和偏置部分谁强谁决定的,你这个放大器组成bandgap是这么接的吗?合理吗?是不是Y点左边应该与OP那边的bias断开?)

蓝色的是一个学长给的建议不过没怎么懂啊?他说的对吗?断开的话偏置只是OP的了啊!

基准方面那样电流怎么设定啊? 而且现在仿真的时由于Y点电位,PMOS改变W/L的值电流也不变?为什么啊?

OP的Y点影响到底是什么?

还有电路的启动部分不会加资料上都是样板,内部的参数都没说!还是说就是那样连着就好啊~我试了一个没效果啊!希望能有人给个详细的电路····

望回复啊

你的电路图是错的,好好看看书吧

y是运放的输出信号

这个信号又回去接了运放内部的负载和尾电流偏执

应该就是这里啦成了鸡生蛋蛋生鸡问题运放的输出又在偏置运放的尾电流...

基准的三极管貌似没有偏置?运放正负接反了

咋一看这个电路有三个问题:

1、EA正负极接反了

2、最右边的偏置没有启动电路

3、第二条红线处运放偏置电流与PTAT电流连线需要断开。

其实这个电路也可以不需要左边的偏置电路。建议LZ多读读paper推推公式问题在于,用于产生VREF的电流源,来源于最左边的bias电路,而非△Vbe/R所以,这是一个原理错误的电路

你学长说的没错

好好看书,打好基础。

水汤汤说的对,自己bias自己容易有问题

LZ先不要急着仿真,先把整个电路的工作原理搞清楚再说,最好用笔画画。

谢谢,我再加上启动电路试试和改改电路,能加下QQ290382687吗?有问题希望你能帮下我毕业设计太难受了···

谢谢我们加一下你的QQ吗有问题希望可以问下你··我毕业设计·苦恼啊··290382687我的号望回复

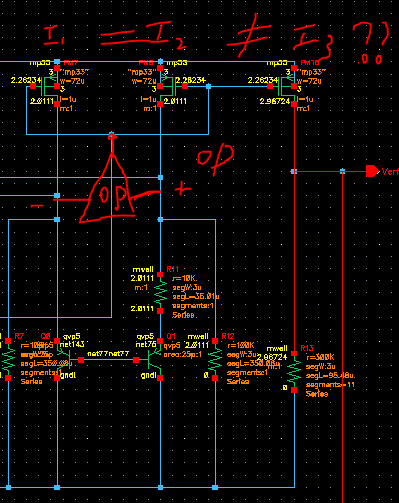

···· 你Y点的电压 由 你的ref电压 除以pmos下面的电阻得出的电流 用在pmos的平方率公式上 得出的你改变pmos当然电流不变

你Y点的电压应该预设成一个合理的值 使得漏端接vref的 pmos能在饱和区比如你是1.2v的电压vref是要0.8vvth算350mv那么 VY就不能小于 0.45v又要保证pmos不截止那么不能超过 0.85v所以0.6-0.65 比较合适一般都设成vdd一半

然后再通过 你想要的vref那条之路上的电流(这个完全由你vref下面的那个电阻决定)算出你pmos的管子宽长比

我可以加你的QQ吗?

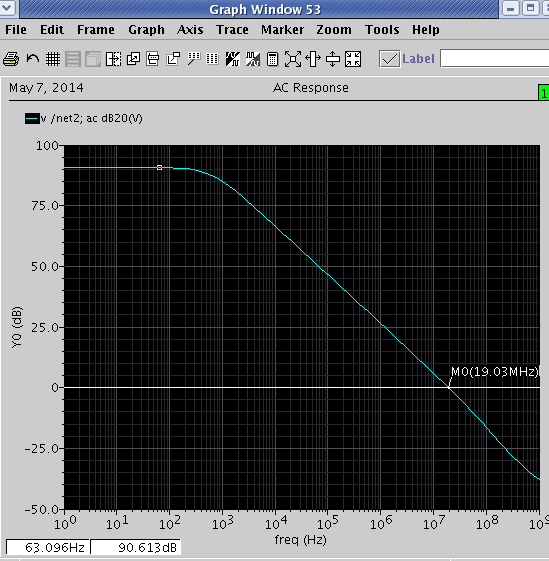

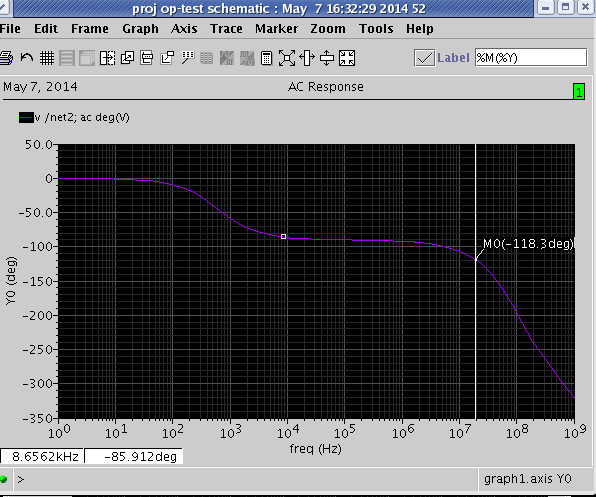

这是我把电路改进后了,但是Verf产生的电路部分上的PMOS不知道为什么它的电流不和前两个一致,而且他们的电流不是应该由下面的I=VBE/R7+(VBE1-VBE2)/R11, 得出与温度无关的电流,对应的求出R11与R7的比值,其中R7=R12。你说的放大器的输出的范围这里是这个问题吗?我仿真结果看这俩PMOS都在饱和区,为什么前两个没事,最后一个I3怎么不和前面相等??

这是我把电路改进后了,但是Verf产生的电路部分上的PMOS不知道为什么它的电流不和前两个一致,而且他们的电流不是应该由下面的I=VBE/R7+(VBE1-VBE2)/R11, 得出与温度无关的电流,对应的求出R11与R7的比值,其中R7=R12。你说的放大器的输出的范围这里是这个问题吗?我仿真结果看这俩PMOS都在饱和区,为什么前两个没事,最后一个I3怎么不和前面相等?这个是不是接成正反馈了,而且OP的偏置电路需要启动电路