关于CDR抖动容限的疑问

时间:10-02

整理:3721RD

点击:

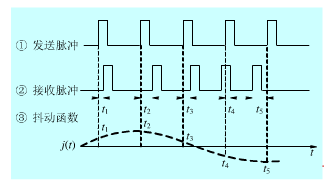

这个是我在网上查的数字通信课件里面的插图

拉扎维的书举了一个CDR的抖动容限的例子,在低抖动频率下抖动容限是峰峰15个UI,是左右个7.5个UI吗?我不大理解的是数据怎么超前7.5个UI,按照我看的数字通信课件,应该超前不会超过1个UI的。

麻烦大侠指导一下,我理解错在哪里了~

多谢!

求帮助啊,或者说哪本书上有讲这个的?本科学的不是这个,理解起来难免会存在偏差呀

求指导呀

7.5UI指的是低頻jitter,在這狀況下傳送脈冲的頻率會緩慢的改變,接收端應採用frequency&phase locked loop因應傳送脈冲頻率的變化區間!

您的意思是传送的脉冲也不断在抖动而不是固定不动的,不只是接收到的脉冲在抖动?

是的,傳送脈冲是動態改變的!

虽然发送的数据可以抖动, 但是接收的数据怎么能超前发送的数据好多个UI,我有点理解不了这个,感觉有点钻牛角尖了

我觉得图画错了,第二个波形<---第一个波形x抖动调制

这里15UI是指相对于一个理想无jitter的时钟基准来说的,例如给这个理想时钟的每个上升沿标上号,那开始时1号沿对着1号数据,如果数据里有jitter 把数据相位一点一点地往后移,每个周期移一点。那经过若干周期,那可能第n号时钟沿就对上了第n+15号数据,这时我们就说数据上有15UI 的jitter。

如果你不管以前的历史,不看标号,一下子就去看第n号时钟,你是不会知道有多少UI的相位差的,因为时钟是周期的。

CDR要做的就是把这个理想时钟的相位动态地根据数据相位的变化进行移动。如果CDR很牛,不管数据相位变得多快,多大,它都能让时钟跟上,那它的jitter tolerance就大。这就是jitter tolerance 的意义。

感谢热心的指导哈,这是我去年的问题,现在芯片都回来测试了哈~