直接连接OTA到pad,结果会如何?

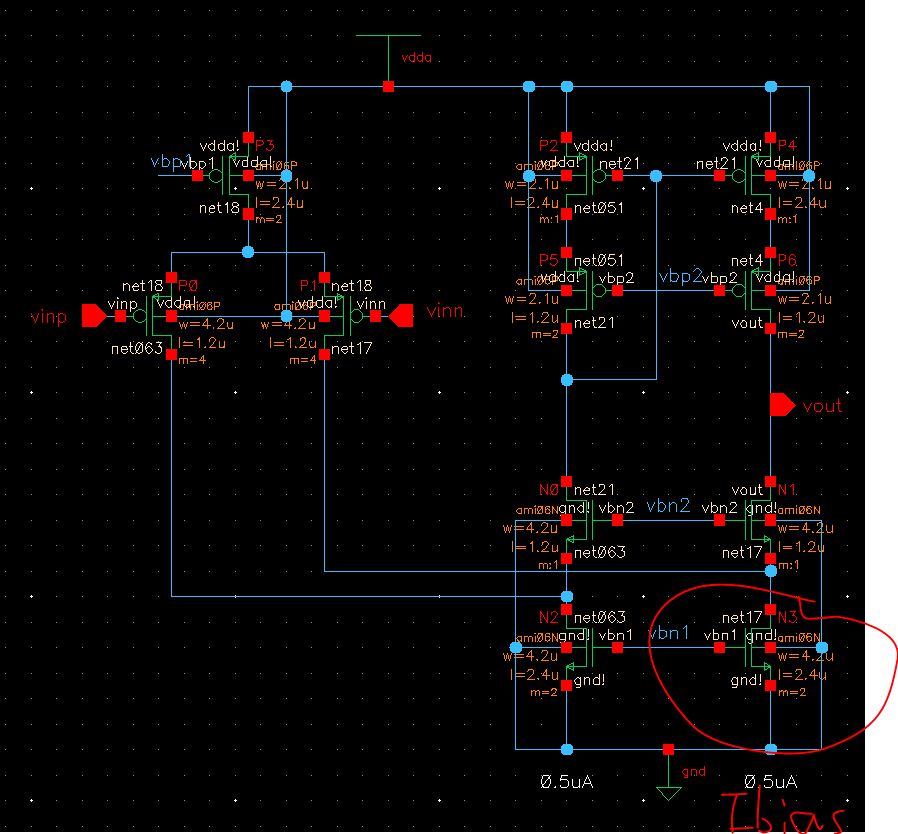

hi,大家好,有一个折叠共源共栅结构的OTA,如图所示,图中N2和N3提供偏置电流Ibias,分别为500nA。 这个OTA输出端为电路中间节点,后级接到一个管子的gate端。

我需要直接把这个OTA输出端接到芯片输出pad,而不使用buffer。这样潜在的影响来自pad漏电流和bonding(压焊)寄生电容电感影响。

pad有两个选择:

1. 使用有ESD保护的pad,这种pad有漏电流,不知道这种漏电流有多大?500nA的OTA是否无法驱动pad?我先使用的ESD pad是使用diode保护,面积是333um2。

2. 使用无ESD保护的pad,没有漏电流。这种pad存在击穿危险. 大家是否推荐使用?

来自pad的bonding(压焊)寄生电容电感一般有多大?

速率不高1不需要考虑外接的寄生效应

1. 主要是要考虑ESD的结构对OTA的影响。最好把OTA和pad连在一起仿一下看看

2.裸奔的危险还是很大的

嗯,多谢回答。

仿一下ESD漏电流是多大,一般不过pA。话说500nA的ota...电源电压多大?连接pad主要考虑寄生电容的影响,估算pad的电容,作为负载电容仿真一下环路稳定性。

另外pad的放置也要考虑,和最终输出端的位置远一点。bonding wire之间的串扰也是比较头疼的事情。

P6和N1需要用ESD rule去layout,或者vout连接一个电阻(几百到几k之间)输出到pad。

但是PAD的ESD最好还是要有,如果只是测试倒是还好,如果是量产,很容易挂掉。

仿真库里面没有ESD二极管模型,但是我刚刚找到测试的数据,算了一下不超过2fA。

500nA的OTA电源电压是5V。使用的是AMI 0.5um工艺。

关于Pad寄生电容,ESD二极管的电容估计1pF,pad双层金属提取电容很小,不超过1pF。不过我对bonding的寄生电容有疑问,这个链接:

http://www.mosis.com/pages/products/assembly/index里面给出的压焊线寄生电容大概0.3pF,寄生电感大约6nH,寄生电容比我想象的也小太多了。我印象中怎么是>50pF?

另外,你提到“pad的放置也要考虑,和最终输出端的位置远一点”, 什么是最终输出端? OTA输出吗?

还有,bonding wire之间的串扰是怎么回事?bonding wire的间距怎么着也比片上的走线间距大太多了,线线之间的电容应该很小,这样寄生电容非常小吧,是什么引入的串扰呢?

你的建议是要用ESD保护。我原帖里提到的是比较担心ESD的漏电流,所以考虑不加ESD保护,不过有人回复说ESD diode漏电很小,最多不会超过10nA,这样对于500nA 的OTA来说,实在太小,漏电流应该对OTA驱动没有影响吧。目前结论是500nA的OTA直接接到有ESD保护的pad,应该没有问题吧。你的看法呢?

我刚才理解错了,你的意思是用ESD rule layout管子,我还是第一次听说,能大概讲讲吗?请指教。

p6和n1的drain端的active拉开一些,每种工艺的ESD rule不一样,有的process需要拉开6um。有可能还会建议在drain端再盖一层rpo。

寄生电容电感的值请参考权威数据。你的OTA是中间节点,最终输出端指的是你的整个芯片处理完的信号输出端,这个端口一般都带有buffer,驱动能力强,信号能量大。对周围会产生干扰。

Wire之间的距离虽然更大,但相比之下长度也要长的多,电感量/互感量也更大。不是只有电容耦合会串扰,互感耦合也会(考虑一下“天线”)。此外,在做精密信号处理的时候,芯片内部的信号线也要做成微带的形式,防止串扰。

顺便提醒一下。CMOS工艺中,Diode是横向的,电流容限需考虑的是内部区域的周长而不是面积。查找一些数据证明你的ESD结构的电流容限足够,面积有限的话,可以做成梳形。

亲,N1和P6不是ESD管,你这样搞的话,这个OTA就挂了。

我当然知道这个p6,n1不是ESD管子,但是ESD打死的却是这两个管子。

你确定这样做OTA会挂掉吗?

你们公司的ESD没有这种要求吗?

esd cell 目地是當發生 esd , 電流流去 esd . 避免留到 core circuit ..但往往 是同metal 下再 ESD 還沒ON

前內部 core circuit 已被打穿

如果你是須要 bonding 出來就使用 IO/ESD rule ,以免生產時掛掉

到時發生 漏電你會無法判斷

到底是本身電路失敗 ?還是因為 ESD 漏電而失敗 ,

因為你這電路應該不確定是否 OK 才會多 PAD .

最好方式是把內部信號使用 buffer 推到 IO PAD ..至少可以確保不是ESD 漏電使電路失敗 .

bonding(压焊)寄生电容电感一般有多大

=> sop8 ~ sot23 package电感 一般是 2n ~

但是 BONDING WIRE越長電感越大還有 一般是 1mil也有 0.8mil

AMI06 process 是那家 Fab ?

非常实际的意见啊,多谢!

有益的讨论,受教了。

我觉得hszgl是如果不使用ESD保护的pad(以避免漏电流影响)的话,需要把N1 P6在layout上做适当保护。而你的意思是不赞成使用无ESD保护的pad,如果这样的话N1和P6会挂掉,即使把N1和P6在layout做适当的ESD保护也不行,对吗?

嗯,是啊,所以我才讨论漏电流的影响,如果影响大的话就用无ESD保护的pad,直接一条线把信号连出芯片。不过通过大家的讨论,我发现,漏电流顶多10nA,对500nA的OTA应该不会造成驱动能力不够的问题。另外我也在考虑寄生电容电感的影响。关于寄生效应,官方给出这个链接http://www.mosis.com/pages/products/assembly/index

在最底部表格里,bonding寄生电感是几个nH,跟你给出的值接近,但是bonding寄生电容只有0.2 pF,真是出乎意料的小了。另外我版图提取(EXtract)发现pad金属走线寄生电容不到1pF,即使加上ESD保护作用的diode的寄生电容,也不到1pF,这样总寄生电容也只有1~2pF,真是出乎意料。你了解的话能说说嘛?

PAD必须(针对量产)加ESD,并且P6和N1用ESD rule去layout。

你用ESD RULE画这两个管子,那么如何保证它们与N0,P5的对称性?ESD rule定义的结构是为了耐压,而且ESD管是PN结反偏,而这两个管子工作在饱和区,保护作用一样么?此外,N1和P6的放电通路在哪里?泄放电荷依然会通过N3和P4,一样存在ESD问题。

即使这样对防止管子被打坏有一定帮助,但是OTA先失效了,岂不是“捡了芝麻,丢了西瓜”?

您对ESD和Layout的理解还需要再加强一下。建议阅读《模拟版图的艺术》

你理解反了,我的意思是N1和P6用ESD rule会引起电流镜的不匹配而严重影响OTA的性能,不可取。

如andy兄所言,ESD结构是为瞬间泄放的电荷构造一个通路,让这些电荷从别的地方流出去,而不让其流经core circuit。

我的意见是量产的话ESD结构必须加。另外这个结构不仅仅只有二极管或二极管接法的MOS,一般还有一个100欧姆左右的电阻,用于隔离大电流。

此外,从放电通路上看,ESD电流不仅会流经N1、P6,还会流经N3、P4,这样看的话仅修改N1,P6无济于事。

要不整个OTA的cascode 都用ESD rule。但我从来没听说过要这么用。

对于ESD, OUT的PMOS和NMOS都要接上ESD电阻才保险的

哎,就到这里吧,不想再说下去了。

2级ESD保护做不做,随你自己了。

還有 PACKAGE 後

引腳間 parastic Cap

bonding wire 本來就是線只是 電感...但電容是IC PACKAGE

nicer

你这样点了一下,我明白了。所以寄生电容应该从package上算。一般package外壳跟地(substrate)接一起。 那么寄生电容包括bonding wire, PAD与package外壳的电容,这部分比较大。

找到了一些资料

这个link

http://e2e.ti.com/support/amplifiers/high_speed_amplifiers/f/10/t/154379.aspx

提到package 总寄生电容2pF~6pF。

这个link

http://www.analog.com/library/analogdialogue/anniversary/21.html

提到bonding wire之间电容0.2pF~0.6pF。

这个link

http://www.intel.com/content/dam/www/public/us/en/documents/packaging-databooks/packaging-chapter-04-databook.pdf

里table4-6 到4-12 也给出了一些pakage寄生电容参数

多谢说明,我现在对于没有ESD保护的pad的使用心里有些底了:是可以用的。