pmos管输出电路,求解答!

时间:10-02

整理:3721RD

点击:

对一个PMOS管仿真,输入参数如下,衬底V=5V,源级Vs=5v,栅极Vg=5v,漏极为输出,接了一电容其电压初始化为0,下面是我的hspice程序:

*Test Circuit*

.option post=2

vdd vdd 0 dc 5v

vin in0 dc 0v

mp1 out vdd in vdd pch l=1u w=16u

cload out 0 1p ic=0v

.model pch pmos level=13

.tran 200m 10

.probe v(out)

.end

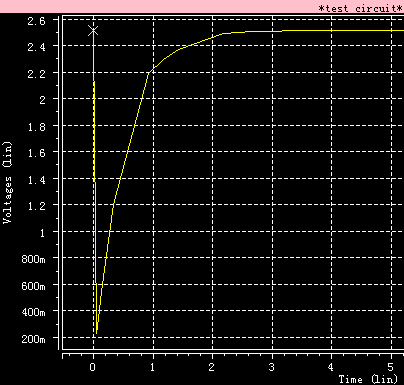

得到的输出如下图所示:

请问:

为什么输出会有个2点几的初始电压?

PMOS管不是应该截止了吗,为什么到后来电压会上升到初始值?

哪位前辈能解答下!

*Test Circuit*

.option post=2

vdd vdd 0 dc 5v

vin in0 dc 0v

mp1 out vdd in vdd pch l=1u w=16u

cload out 0 1p ic=0v

.model pch pmos level=13

.tran 200m 10

.probe v(out)

.end

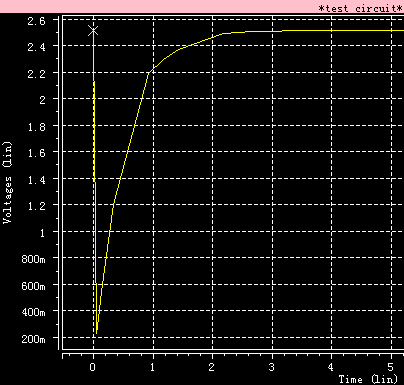

得到的输出如下图所示:

请问:

为什么输出会有个2点几的初始电压?

PMOS管不是应该截止了吗,为什么到后来电压会上升到初始值?

哪位前辈能解答下!

谁来帮帮我!

我是小菜鸟,不太懂

如果不影响功能,就先不要处理这个现象。

这里有点疑问:为什么瞬态不从0开始?

电容电压抬升猜测是PMOS的寄生diode漏电导致。