仿真遇到问题了,SOS!

时间:10-02

整理:3721RD

点击:

本人用Hspice仿真一电路:PMOS管,栅极V=5V,源级V=0V,衬底V=5V,漏极电压为输出,并外接一电容,电压初始电压为0;

仿真结果却让我感到不解:

漏极电压V后来升到2.5V,这是为什么?

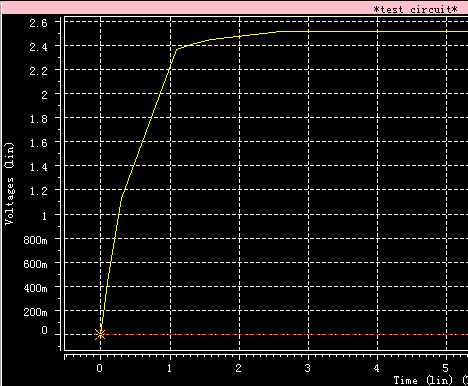

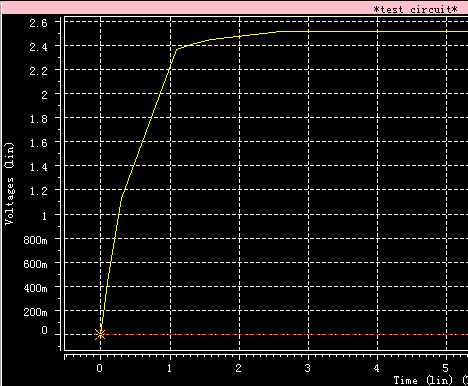

下图是我的仿真结果图,黄色线为漏极输出电压:

附上我的Hspice程序:

*Test Circuit*

.option post=2

vdd vdd 0 dc 5v

vin in0 dc 0v

mp1 out vdd in vdd pch l=1u w=16u

cload out 0 1p ic=0v

.model pch pmos level=13

.tran 200m 10 uic

.probe v(out)

.end

求高人指点,已经对这个问题想了一两天了!

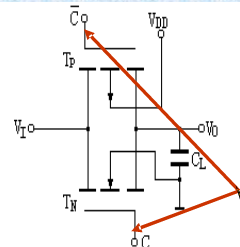

其实我是想仿真这个传输门:

当C=VDD,C反=0时,传输门导通,这时工作正常;

但是当C=0,C反=VDD时,传输门应该截止啊,但是有1点多的输出电压!

于是我就觉得问题出在上面的PMOS管上,单独对PMOS管进行仿真,发现情况果然和我想的不一样!

请问各位,如何解决这个问题啊?

仿真结果却让我感到不解:

漏极电压V后来升到2.5V,这是为什么?

下图是我的仿真结果图,黄色线为漏极输出电压:

附上我的Hspice程序:

*Test Circuit*

.option post=2

vdd vdd 0 dc 5v

vin in0 dc 0v

mp1 out vdd in vdd pch l=1u w=16u

cload out 0 1p ic=0v

.model pch pmos level=13

.tran 200m 10 uic

.probe v(out)

.end

求高人指点,已经对这个问题想了一两天了!

难道通过寄生二极管漏电导致?

应该是电容分压,第一个串联电容的一个极是pmos的栅和衬底,另一极是漏端;第二个串联电容是外部负载电容。

其实我是想仿真这个传输门:

当C=VDD,C反=0时,传输门导通,这时工作正常;

但是当C=0,C反=VDD时,传输门应该截止啊,但是有1点多的输出电压!

于是我就觉得问题出在上面的PMOS管上,单独对PMOS管进行仿真,发现情况果然和我想的不一样!

请问各位,如何解决这个问题啊?

谢谢你的回复,请问你有什么解决的建议吗?

你仿真传输门时初始条件设没?有可能是因为初始条件的原因。我在仿真D触发器时就遇到过初始值为0.9V的情况

同意电容分压,应该是Vgd吧,Vgb是给短路的。

与电容分压没有关系,这是一个dc就能仿真的特性。前面kxjxxfei的说法应该是正确的,二极管漏电流造成的。

电容初始值设为0了呀,还需要设置其他的吗

你仿真的D触发器用到传输门没有?