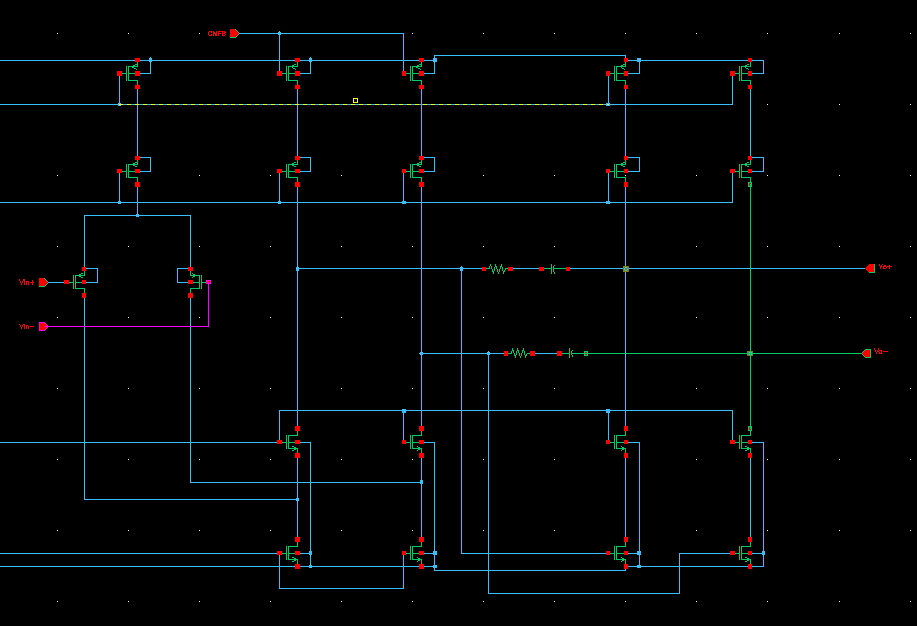

两级运放的瞬态响应问题带图说明?

带多大负载

你现在有没有加负载?现在这PM有点低,估计也就不到50°,输出建立的可能会比较慢。在采样保持电路中能不能建立还得取决于你的采样频率,如果频率过高,用来settle的时间过短,建立可能是个问题。

你给的信息太少,没法判断。

带了一个2p的负载,我在想,第二个极点那对瞬态有没有大的影响,现在在带外,GBW为700M,-135°为1.1G左右,这个极点会不会对瞬态产生较大的影响,采样频率为60M的话,能不能建立

2p的负载电容,主要是想看看瞬态会不会成功,并且担心第二个极点会不会对瞬态产生大的影响?

看来只有自己顶了

瞬态能不能建立还是要跟你的应用环境有关吧,你这个运放打算用在SH,还是MDAC1orMDACN?负载2pf怎么确定的,如果是10bit,这个电容足够大了,但如果是12bit,这个负载电容估计的是不是有点小,确定了负载电容后,判断带宽够不够还是要和采样频率有关,频率越大,对带宽要求越高,现在采样频率是60MHz,这个带宽应用在SH中足够了,另外你说的次极点影响,这个只要保证足够PM和GM就够了吧

谢谢您的回答,我这个运放,我目前想放在SH电路中,负载放了一个2pF的电容,另外有人说,两级运放如果第二级采用共源共栅的话那么SR会特别不好,不知道会不会成为我瞬态建立时间的阻碍?如果是MDAC1的话,负载电容应该放多少,2.5p?我做的是1.5bit/stage,希望你给指导一下?

问题是他的PM不够高,可能都不到50°,输出的建立过程会震荡,所以次极点的影响应该会有

为什么PM会不够高,从什么地方看出来不到50°的,负载2p的时候,DC仿真出来显示的PM是62°,难道这个不太真实?大神解释下?谢谢

您能指导一下怎么看出来PM不够高吗,现在DC仿真放2pF 的负载,波特图中显示的是62的PM,难道还有其他方面我没有考虑,大神解答一下?谢谢

大神,怎么看出来PM不够的,我DC仿真的,2pF的负载,显示的PM是60多度,应该够啊,你为什么说PM不到50°,难道我有其他的因素没有考虑到?望大神给予回复,谢谢

怎么回复不了了,大神,我DC仿真中显示的PM是60多度,为什么您说我的PM只有不到50°,难道还有其他因素我没有考虑到,希望您能给予解答一下》》?另外,我采用的折叠+共源共栅结构,瞬态仿真会不会对SR有影响,据说这种结构会影响SR的大小?谢谢

最近也要做一个 SH 电路,并且是可以变增益的。50M 的采样频率。建立在12bit精度。

我也想问 前几位说50度不到 是怎么看出来的 ? 你不是负载2pf情况 下 仿真的么?还有SH 反馈系数是多少?闭环的带宽也须要考虑吧?、

还有你的带宽和sr没有算过吗?

会持续关注这个帖子。希望与小编多交流。

先问问自己settling time的要求怎么来的,先看看运放再来做adc

第二级用共源共栅结构的我也不太清楚,我在论文上也没见过,你放到里面试试吧,另外如果SH负载是2PF,MDAC1怎么可能是2.5PF,肯定会Scaling down啊

路过围观,求大神

guanzhu