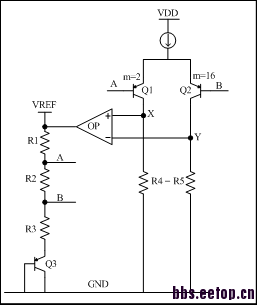

一个基准电路

电路中R4=R5

优点?没看出来。

谢谢了……

我水平有限。只是感觉原理上没区别,结构上的区别只是表层的。

减小运放输入端OFFSET影响

不错,如楼上所说可以减小运放offset

psr有没有提高呢

能够说说怎么减小了运放的offset?我不了解

坛里的朋友有没有遇难过基准没有补偿的情况下,温漂曲线是这样的!

不知道是怎么回事,图片上传总是失败,就描述一下吧:基准电压从-40度开始下降,大概0度的时候又开始上升,到60度左右的时候又开始下降。形成一个波谷和一个波峰状……

低压应用,运放的输入貌似很低很低。我见过用buck作输入的这种运放结构。

你把电阻用理想电阻来代替也是二阶补偿的曲线么?

谢谢你的关注!这个我还没有试过,但我今天减小了一下偏置电压,情况好很多了,但是PTAT电流有点小,25度时只有3.5u!达不到我的设计要求……我的要求是PTAT电流要在6u左右,但是电阻的长还不能太小,这就是个矛盾,要增大电流值,就必须减小电阻,这就不得不减小电阻的长度(电阻的宽度已经是不能再小了)!不知该怎么解决这个问题……

减小电阻,并不一定非要减小尺寸,你可以试一试并联较大的电阻。

减小电阻值应该增加电阻宽度。

你LDO里面用这个bgp?你用什么工艺?BICMOS?

优点:低电源电压

缺点:Low PSRR,BICMOS/BCD工艺限制

low PSR 你是看出来的还是仿真验证的?

如果看出来的,能给出推导?

光看的话,我不觉得这个电路PSR差,相反还挺高的。

人家TI做出来的温度系数最大值是100ppm,精度最大是-+0.1%,噪声d典型值35uVrms(10--10KHz)。

看着还可以啊

TI用这个做单片基准电路?还是TI某个产品里的基准?

单片基准源。

这个你们也reverse 过啊

通过仿真可知其电源电压是很低!但是PSR应该不是很低吧!

TI做过这个电路吗?请问是哪个片子……

1/2β的尾电流会流过A,B两点,所以Q1,Q2的β高好些

我在想,这个电路Q1Q2的基极电流怎么办。

两个问题:1、这里运放的作用是不是只是钳位R4,R5的电压相等?有没有其他作用呢?

2、到底是如何减小offset的呢,这个不明白。

这个bandgap结构很不错,它把电流匹配和bandgap产生两路电路分开。这样可以大大减小运放的input Offset对于bandgap输出的影响,,,可以提高bandgap的样品正太分布,进而提高产品的yield。 如果电流匹配和bangdap两路合并,并通过运放clampXY两点,那么运放的输入offset会被严重的放大,影响良率。

PSRR的优点,不明显,整个环路依靠运放的大dc gain来实现大的PSRR以及open loop gain。dc gain 越大,闭环loop更接近于1,也就是输出的bgr精度越高。只要有运放clamp,PSRR都不会差。最大的优点是OFFSET。小编可以自己推到下,点到为止。