请问选题方向

请问做哪个好呢? 从今后找工作,发文章等方面考虑。

谢谢

可以先去网上调查一下嘛,哪个难度比较大,或者哪个比较有新的地方可以考虑,要不问你boss,最直接了。

建议做C-T ADC,20MHz信号带宽,能够做到下面这篇文章就行

A 20-mW 640-MHz CMOS Continuous-Time SigmaDelta ADC With 20-MHz Signal Bandwidth, 80-dB Dynamic Range and 12-bit ENOB,JSSC Dec. 2006

PLL和C-T ADC能够构成一个完整的系统。

多谢楼上二位。

CT SD ADC要做的话主要就是解决jitter和非线性的影响,使它更稳定。

PLL不是很清楚,是不是高频(>50GHz)是设计的方向?

ADC的jitter问题就是通过高性能PLL解决的。

如果要得到12-14Bits C-T ADC的话,片上PLL是必须的。

对于一个博士课题来说,作一个20MHz CT SD 加上一个0.5ps jitter PLL 实在太多了。

没见那个paper有多少个co-authors,而且都是工作N年得人。

选课题也要量力而行。

这2个课题,任何一个作明白得都很好

CT ADC FOM 要能做到0.3pj/cov 以下都是肯定可以进JSSC了

呵呵,ADC在PLL中的应用也越来越广,所以说这两个课题都不错嘛

我想调运放,给个指标吧

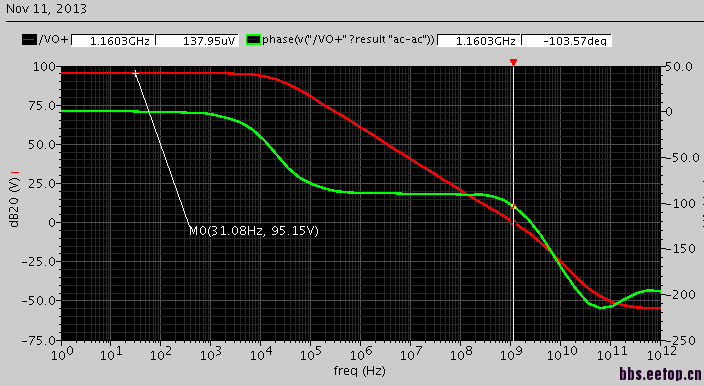

DCgain>90dB, GBW>1GHz, PM>72deg, Power<2mA, CL=1pF, 试试看。

zwtang

2013/11/8

高桥君多谢大牛!

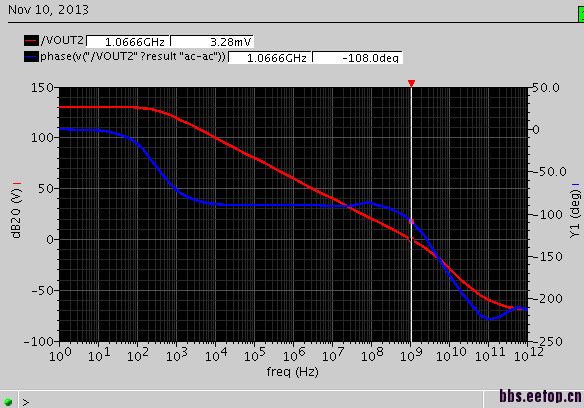

看看这个行不行,主运放采用NMOS input pair telescopic cascode结构,外加gain boosting 提升低频增益,全差分形式,VDD=3.3V,smic.13工艺,增益带宽仿真是在VCM=1.5V的情况下仿的。主运放消耗电流1.8mA,4个辅助运放共消耗电流80uA,CMFB消耗电流100uA,DC gain=130dB,GBW=1.066GHz,PM=72°。

提供数据,不多不少,刚刚好。

但电路图看不清,不好说了。比如,可能换个工艺角就不行了。

PLL更好找工作

发错地方了

实现这种指标的运放用什么结构最合适?

工艺角跑了,在125度高温下GBW降到900MHz,修改了电路后功耗增加至2.1mA,corner角都能过了,最差GBW=1GHz,最好的时候有1.5GHz。

图看不清,不好瞎猜(看着有很多理想源),解铃系铃,唐老师来判断行不行。

0.13um 工艺能否采用1.2V电压或者1.8V,3.3V太高了,难度降低了。

整体性能还不错!CMFB能否采用SC结构,整个Opamp放置在一个SHA电路中进行性能仿真。

zwtang

2013/11/10

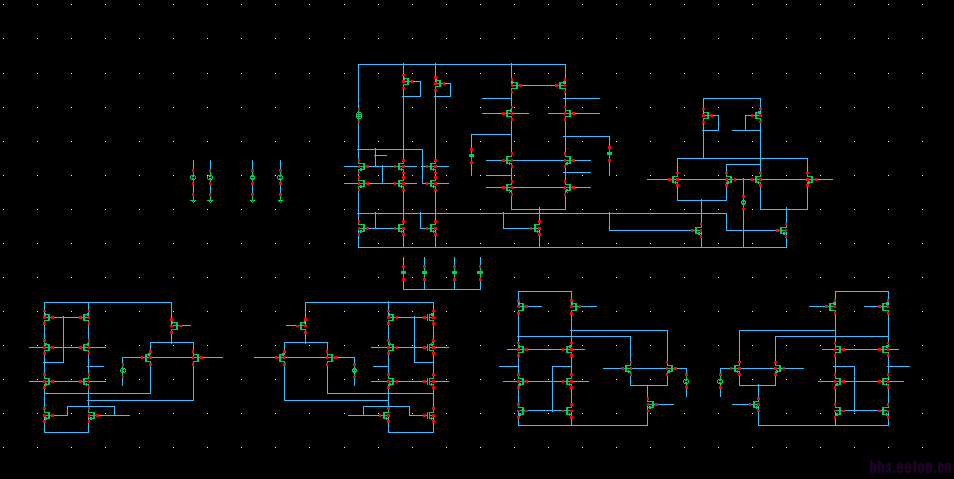

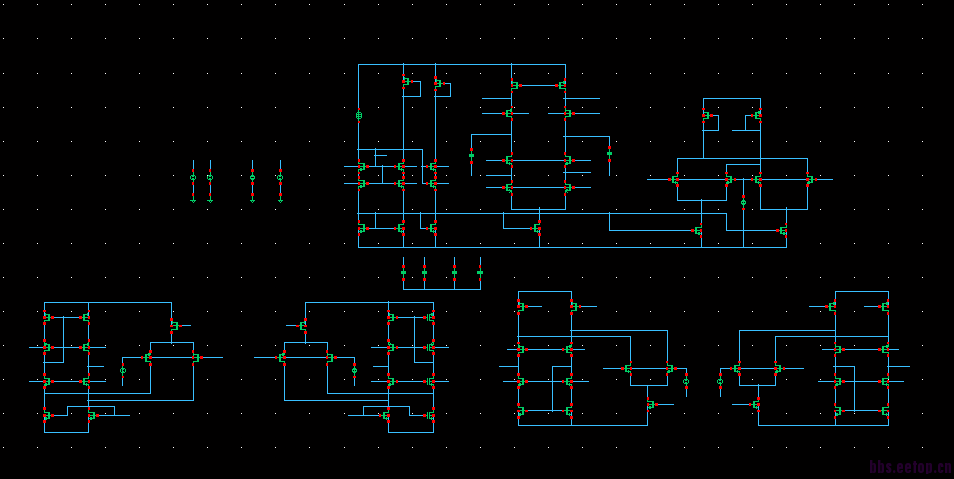

四个辅助opamp可以减成2个,还有一点,难道想把整个芯片做成flatten的schematic。

好,我再试试哈

确实可以减少2个,版图不会考虑

schematic要做的整洁漂亮,一眼就能看清楚,辅助opamp可以做成symbol,而且在不同电路里可以重复调用。做电路时候最好考虑一下layout,做电路时候版图就能清晰出现在脑子里,需要多大size心里清楚

我确实没做成symbol,至于版图,没画过模拟版图,

我一直坚信自己做的layout比layout engineer做的更好更优化,有时只是忙不过来或不值得自己亲自去做罢了,但是designer要对chip负责的,所以还是要懂点layout的

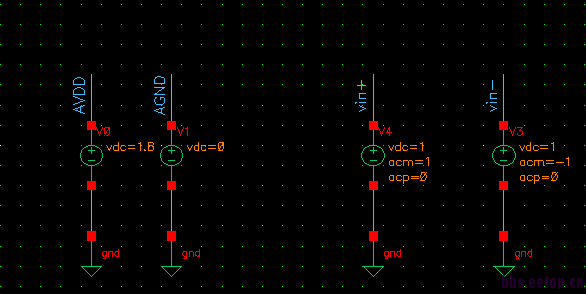

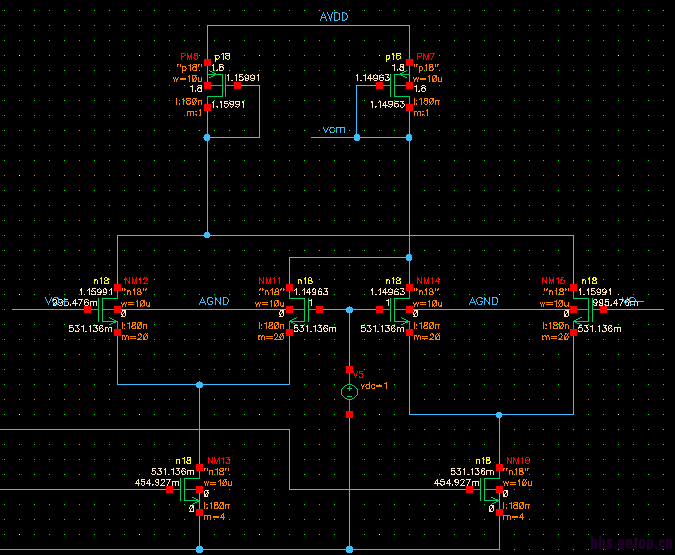

看看我这个电路,工艺是smic.18的,电源电压降到了1.8V.

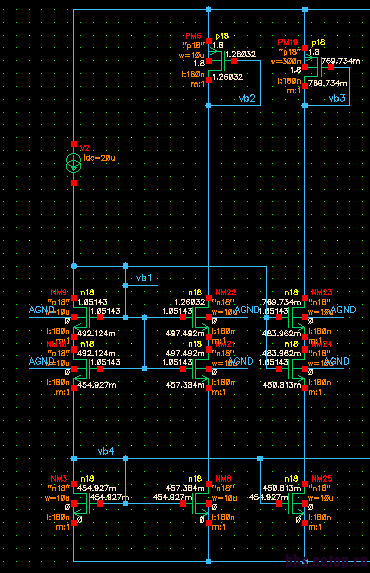

偏置电路镜像20uA的电流给其他模块

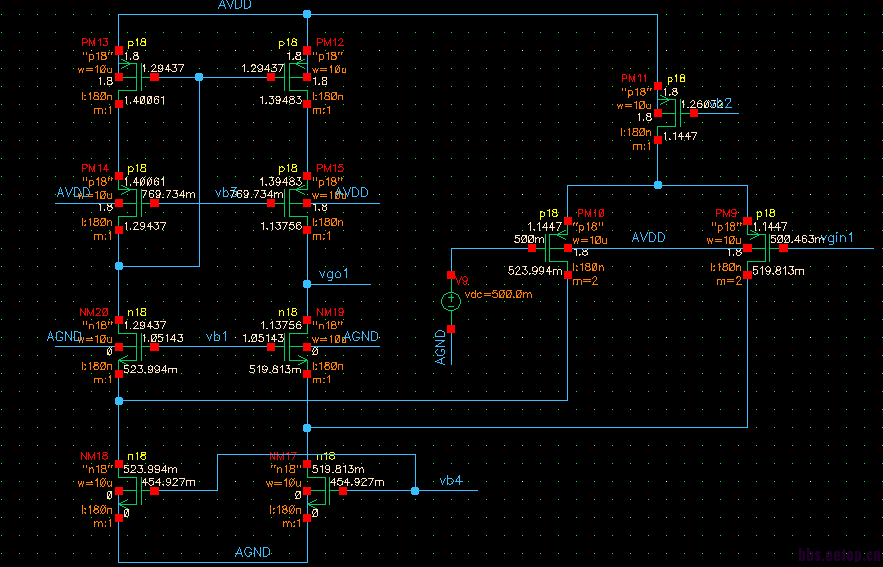

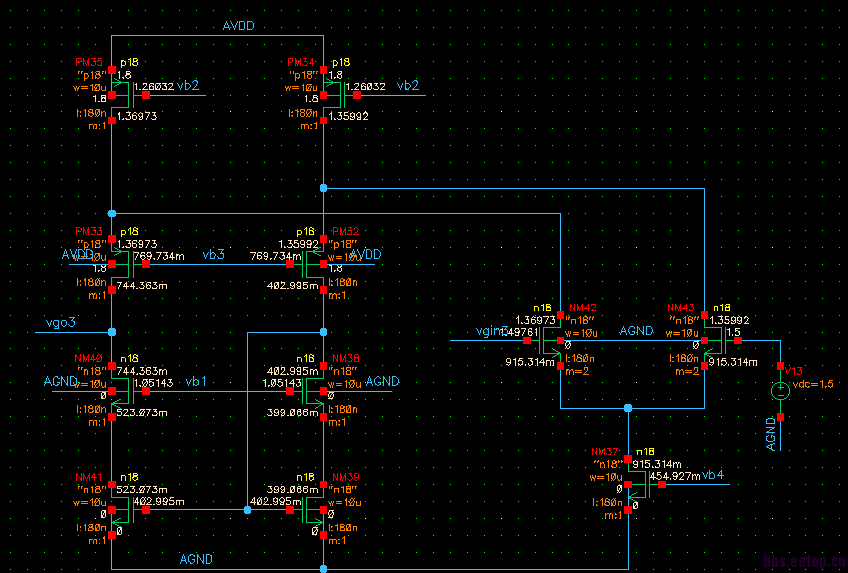

主运放采用NMOS输入管,套筒式共源共栅机构,全差分输出。

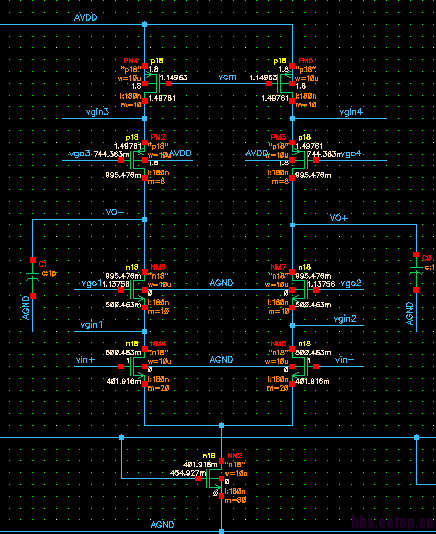

两个辅助放大器都是折叠式共源共栅结构,作为gain boosting的运放来用

为了消掉GBW附近的零极点对,在辅助运放输出端接了100fF的小电容。

共模反馈结构如下图,输出点共模电压为1V。

总电路如下

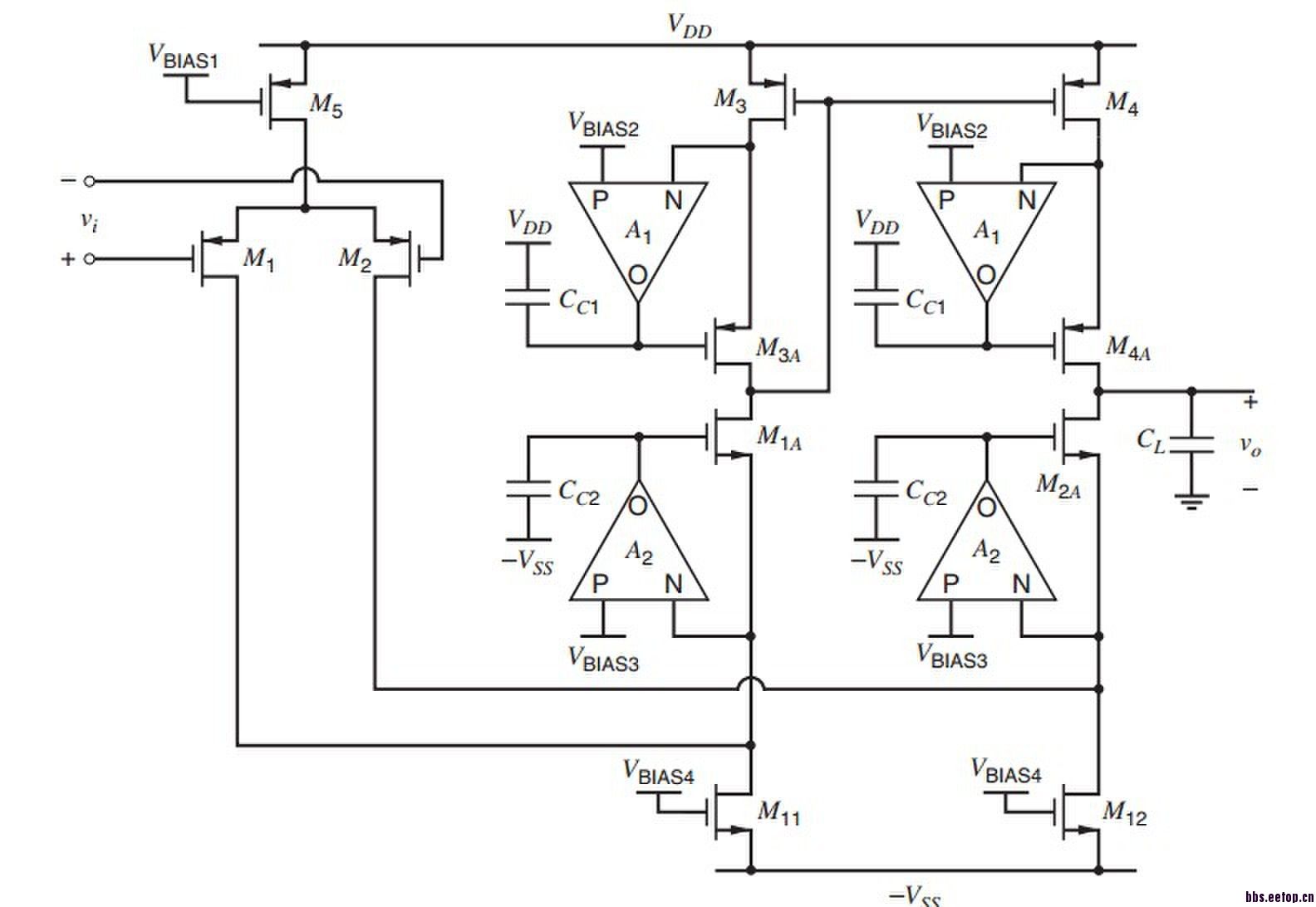

仿照格雷书上的电路,原图如下,单端转差分

仿真结果如下

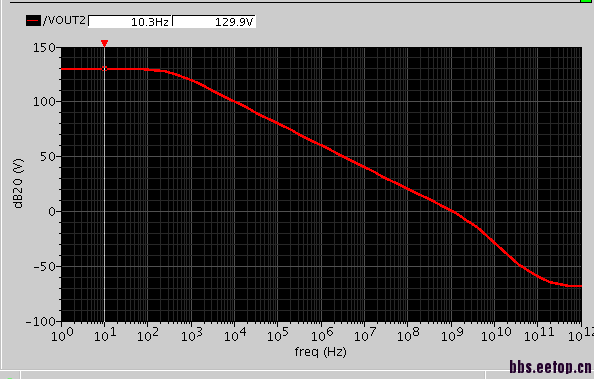

GBW达到了1.16GHz,DC gain=95dB,相位裕度为76°。主运放消耗功耗1.6mA电流,其余加起来0.28mA,总共是1.88mA,所有指标都是在TT常温下仿真的。

我有一些问题:

1:我用的工艺是smic.18的,没有用RF管子,前仿可以达到1GHz的带宽,版图画出来后,流片出来后真能达到这么大?

2.为了实现搞带宽,所有管子的沟道长度都取最小值L=180nm,运放输入管也取了180nm,这样行吗?L取得这么小,高阶效应建模就不准确了,完全就不是那么一回事了。如果运放输入管L取2um,那么带宽肯定不会到1GHz.换句话说,实现1GHz的运放,用什么工艺最合适?

看我25楼的帖子哈

这种电路没有什么实用价值,用来练练手的。

搭积木式设计。

上面那哥们不跟你说了么:增益增强OP用全差分,可以省两个。

我懒得改了,哈哈。我也觉得搞模拟没意思,感觉实际和理论差距太大了,我就是想混口饭吃而已,不做学术。

怎么没意义呢? 我觉得lz做的挺漂亮的。

他能做好这一个,做别的肯定也行啊。

还有,小编你现在在做啥啊? 怎么一直研究OTA?

OTA东西上手就行,读研的话还是去做点新一点的东西,别人没弄透,或者弄的不多的地方啊。