全差分运放中对共模反馈结构的性能有什么要求,又是对波形的失真有怎么样的影响

各位朋友大家好, 我做的这个运放要应用于12bit的ADC中,由于所用到的时钟信号是40MHz,所以仿真再加上40MHz的信号作为输入时,第一级运放的输出波形会出现失真,而且共模反馈结构对波形的形状有较大影响。(本人认为波形的失真其中之一的原因是SR摆率较小造成的,除了可以增大第一级运放的总电流,并不知道其他解决办法),本人不了解共模反馈结构的性能应该与第一级运放如何匹配(应该达到怎样的要求?),共模反馈结构的宽长比又应该如何设定?还是说有些其他的参数需要注意,比如说是否对其电流大小有要求或是怎样?波形失真又应该怎样调节?望大家一起讨论,请高手做以指导,还望详述

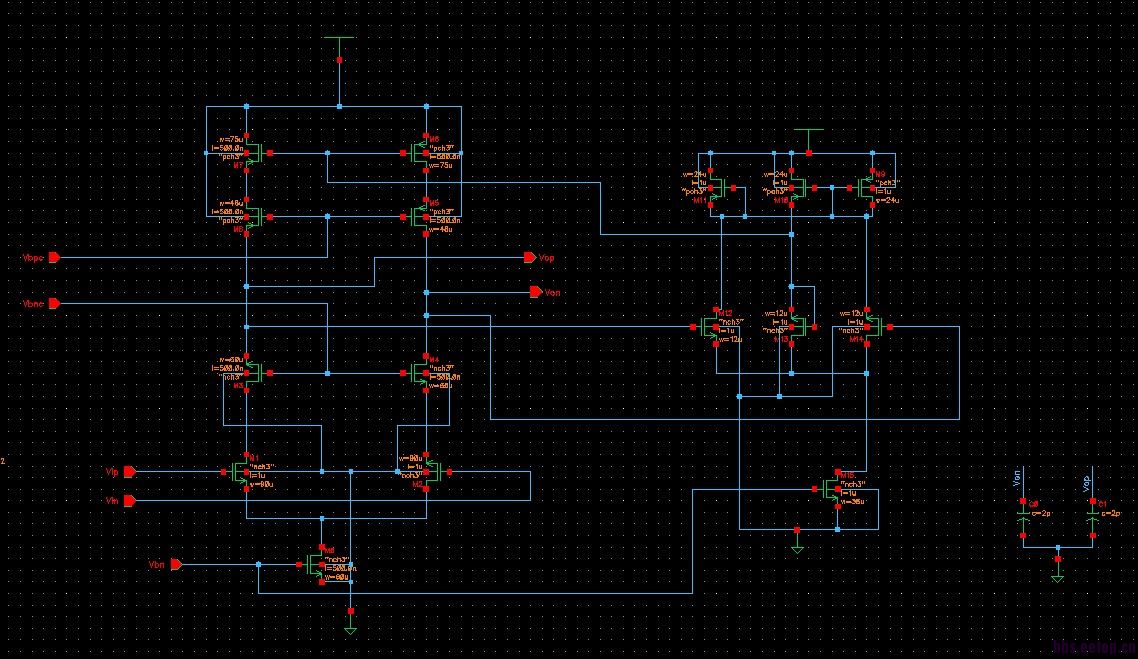

此黑图为第一级运放和其CMFB

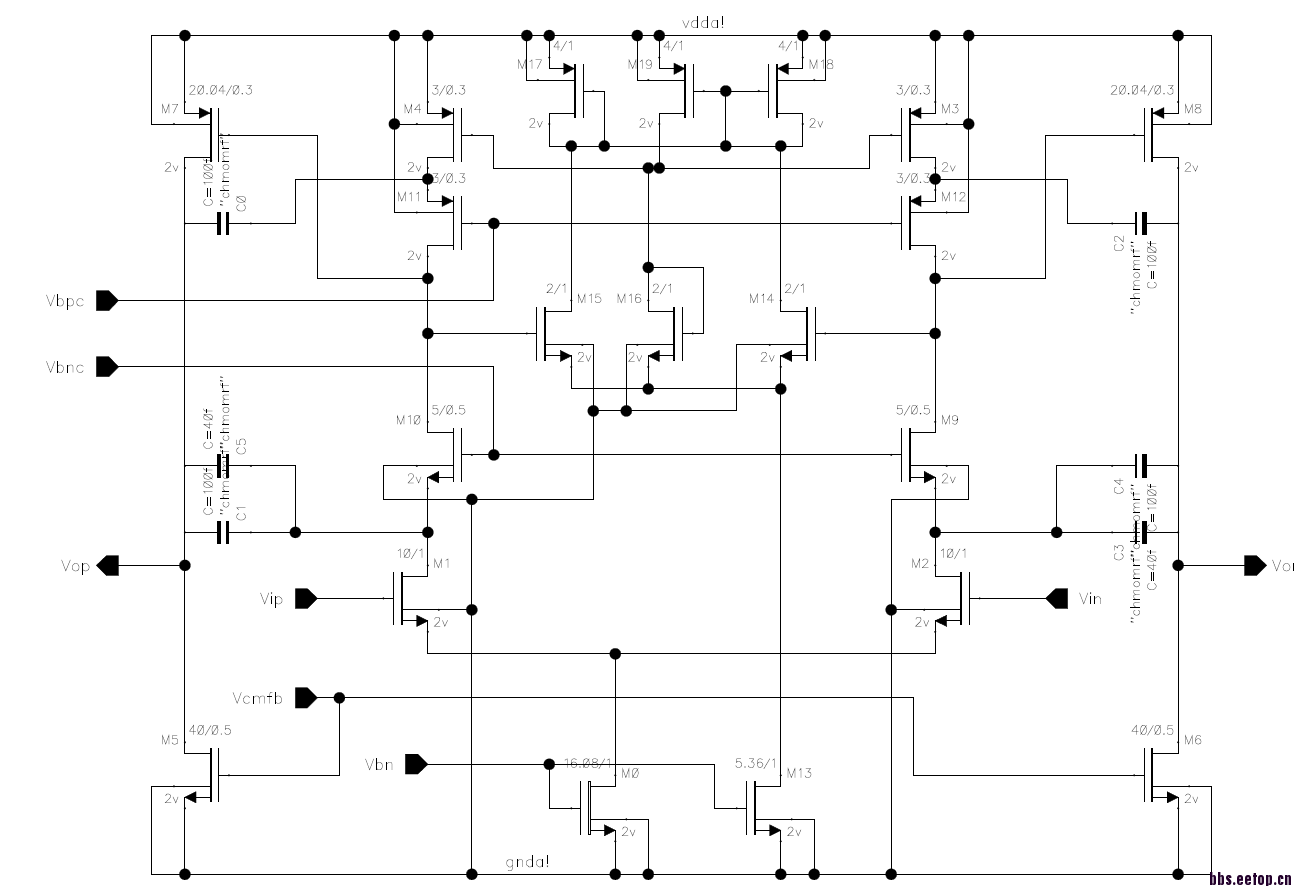

此黑图为第一级运放和其CMFB 白图为两级运放结构及其第一级共模反馈

白图为两级运放结构及其第一级共模反馈

两个问题:

1.你是如何确定失真是由CMFB引起的?

2.既然知道失真是由CMFB引起的,为何还要用这种结构的CMFB?

这种结构的CMFB线性度本来就非常的不好,很多地方都有讨论到

还有两个问题:

1.你的CMFB能引起多大的失真?有没有通过仿真得到有多大的失真?

2.你认为是由SR引起的,那么你是如何通过仿真确认的?

看起來是telescopic 1st stage + common source 2nd stage,

1st stage 採用continuous cmfb,2nd stage的cmfb沒畫出來,應該是switched cmfb,

雖然continuous cmfb有很多缺點

但如果你的power supply=3.3V and 第一級swing很小的條件下

應該堪用

這opamp是12bit pipeline adc的first stage MDAC的opamp嗎?

波形產生失真的圖貼上來

或許能幫到你

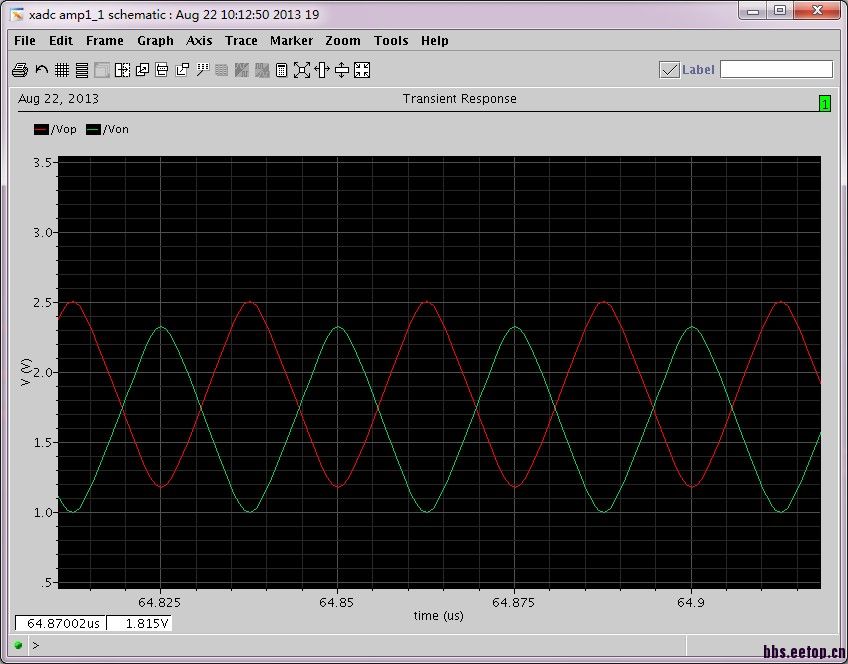

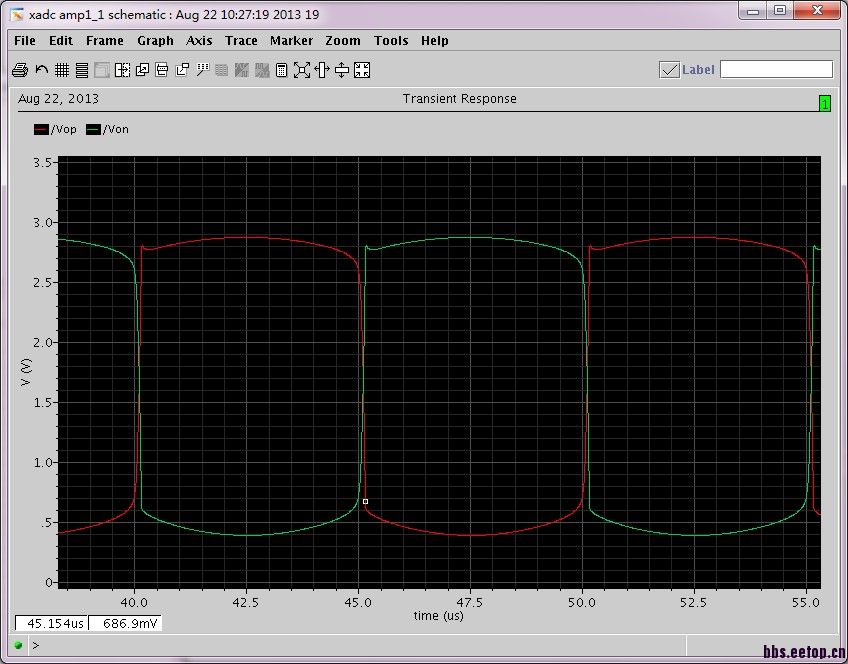

结构是给定的,对于波形的失真,我现在只是从理论上分析应该是与SR有关,波形看着就不是正弦也没有一段电压稳定的时间,当我调小输入信号的频率时,波形就会出现一小段稳定的时间。对于这个问题我一直都不知道怎样入手?还望指导

谢谢了 !

这个是40MHz正弦时的输出波形(无CMFB)

这个是100KHz正弦时的输出波形(无CMFB)

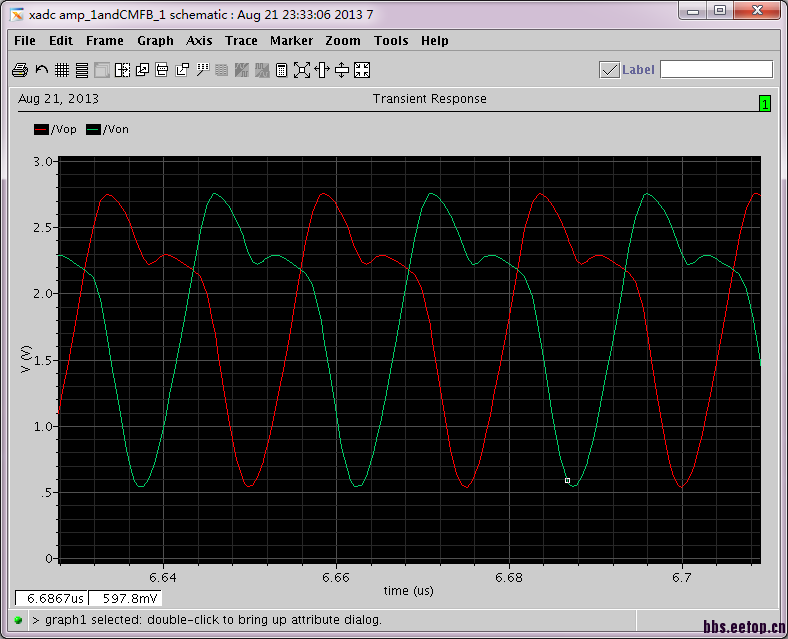

这个是40MHz正弦时的输出波形(加上CMFB)

一般接成CLOSED LOOP後

第一級swing的需求很小

因此可以採用TELESCOPIC OP

也因此不須仿真那麼大的swing

OP跟CMFB OP都脫離飽和區了吧

另外你這仿真有意義嗎?

為什麼要跑這仿真

你這ADC是哪種ADC

恩。支持楼上的说法

我并不知道这个的波形失真与否,会不会影响后面的电路,看好多论文上也没有仿真这个第一级运放的波形的,是不用管它吗? 还是影响不大,又或是怎么样啊?还是说我只要直接去测他的SR是否满足要求就可以了?这个是流水线结构的pipeline-ADC,这个运放主要作用就是将前面数据的余量乘2

1.根據你Vref spec是1.? Vpp 來check 你的2nd stage output swing,mos有無脫離飽和區

2.檢查feedback factor=2時,你的closed loop phase Margin>60,DC Gain>80dB

3. slew rate跟GBW能滿足12 bit settling time

4.Common mode Feedback loop的DC Gain>40dB即可,PhaseMargin>60

之前你跑的仿真沒意義

因為MDAC實際SETTLING的波形跟你仿真的波形差了非常多

非常感谢! 回复的有点慢,这段时间刚刚回来,所以没注意到。

还请问共模反馈环路到底应该如何仿真(测试电路应该是怎么链接,如何加激励)?感觉您对ADC的设计甚为了解,是否有一些资料方便学习的,还请指导。