VCO和PLL的相位噪声问题

时间:10-02

整理:3721RD

点击:

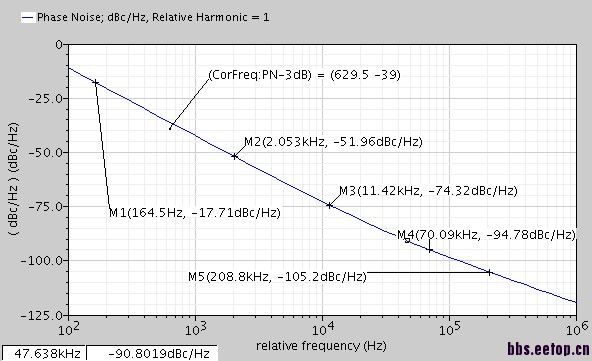

最近测试一个接收机中的VCO和PLL,其1MHz频偏处的相位噪声测试值与设计值差别较大,仿真值能到-125dBc/Hz,但测试值只能到-100dBcM/Hz左右,且更大频偏处的相位噪声也不再改善,均为-100dBc/Hz左右。VCO和PLL(环路带宽为100kHz)的测试情况比较类似,且PLL的带内相位噪声与仿真值差别很小(3个dB以内)。这是不是说明电路的噪底比较差?或者我的测试端口幅度太小(约-42dBm)?有碰到类似情况的朋友吗?

之前我碰到过带外相位噪声不衰减的情况,后来发现是测试仪器的问题,让人来修的,请确认下这个

顺便问下PLL的相位噪声你是怎么仿真的,用什么软件,建模然后把所有模块加起来?

您好,我想问一下,你的振荡中心频率是多少?

-42dBm,幅度太小了吧?我测试的时候感觉幅度这么小的话测相噪没意义,恶化的非常明显。先想办法把输出幅度增大再说吧。