LDO欠冲问题

时间:10-02

整理:3721RD

点击:

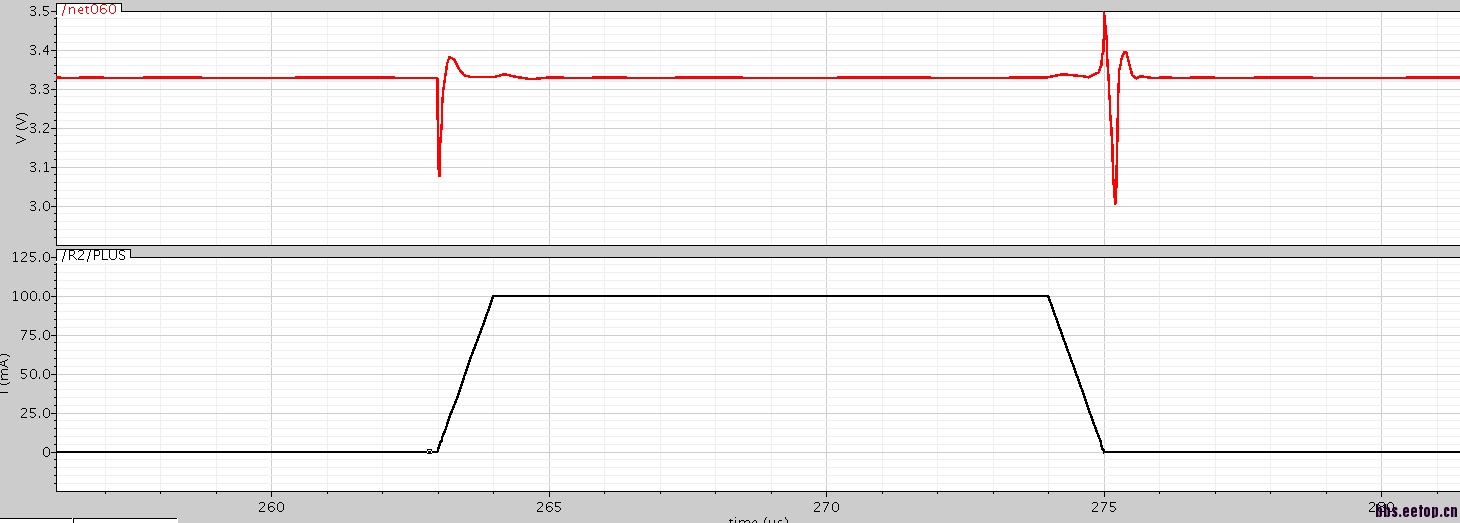

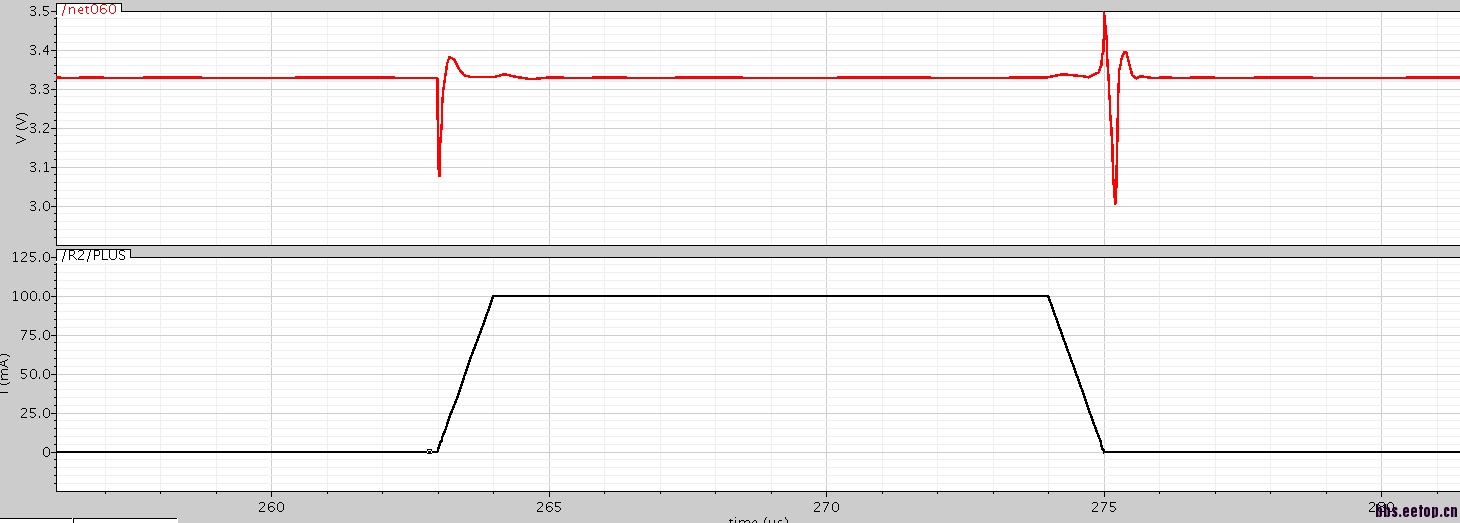

我现在再调一个Capacitorless LDO,仿真时遇到个奇怪问题:重载跳轻载时的欠冲大于轻载跳重载时的,下图所示,为瞬态特性:

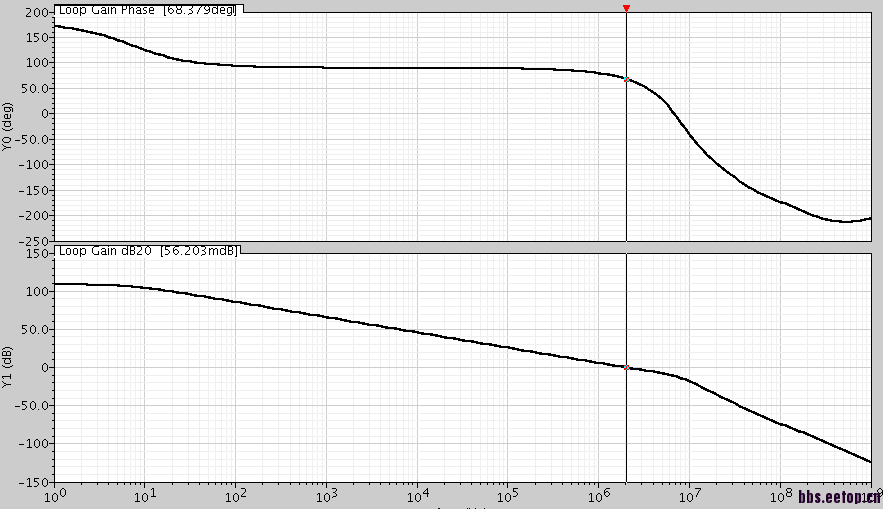

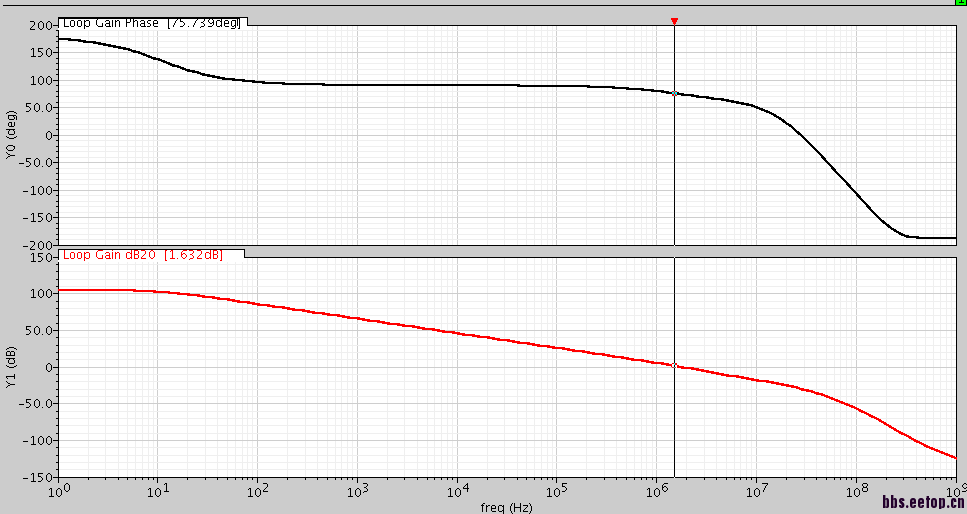

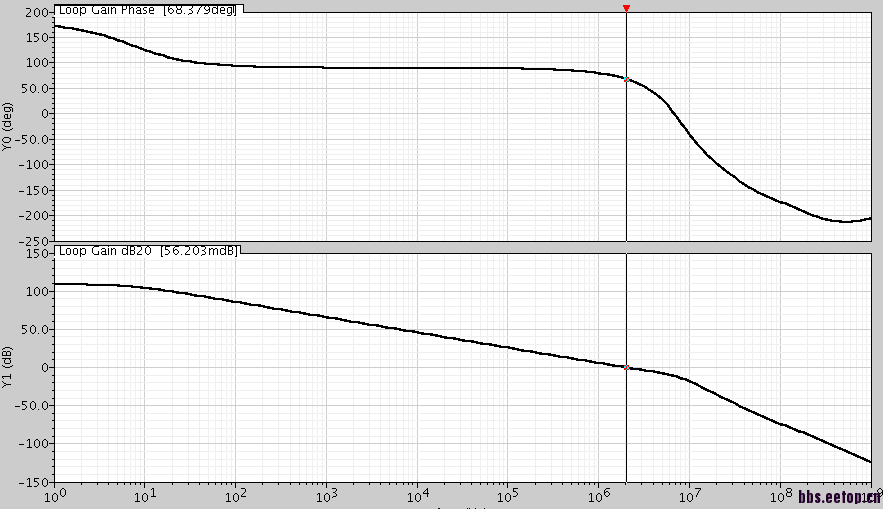

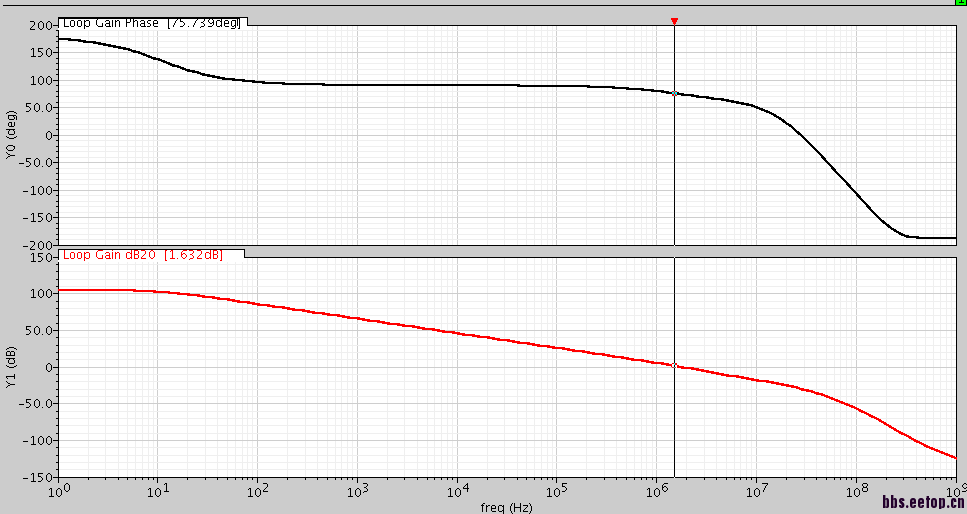

这样的原因应该是重载跳轻载时的过冲反馈后引起的欠冲,我的第一直觉是可能相位裕度不够,但仿真相位裕度都是没有问题的,轻载68,重载75.

自己是新手,不清楚产生这种情况的原因是什么?还请各位指点迷津,谢谢!

这样的原因应该是重载跳轻载时的过冲反馈后引起的欠冲,我的第一直觉是可能相位裕度不够,但仿真相位裕度都是没有问题的,轻载68,重载75.

自己是新手,不清楚产生这种情况的原因是什么?还请各位指点迷津,谢谢!

我假设你的LDO输出管是PMOS,然后前级OP是NMOS作驱动管,然后PMOS做电流负载。

那么你遇到的问题就是前级OP的SR不一样所导致的。

当PMOS管的电压需要上拉(从重loading到轻loading),是靠PMOS管提供的电流来驱动。这个电流是由电流源大小决定的,其SR不会大。另外一种情况是NMOS管下拉,其SR很大,所以可以快速反应。

其实这是一个大信号的过程,小信号ac仿真不能够说明问题。

好想法!不过应该是功率PMOS关断很快,打开较慢?

另外小编的重负载还存在过冲,看上去应该是50度左右(一般情况下)吧?

谢谢xuriver2012 指点迷津,我的PMOS功率管的驱动是ClassAB的,刚检查了,ClassAB的工作点有些问题,导致SR不匹配。

这个做的很漂亮.

董怀鹏~这个名字好熟悉

性能还是比较差,而且PSR差,路漫漫

学长好

路过,学习

正好遇到这个问题,正好是学长发的贴

Class AB 可以解决这个问题

再mark 一个。