PLL 锁定问题

期待各位大神的帮助指导,感激不尽!

很厉害死啊你 学习学习

你这都到达了让人想死的SPEC级别了,各种参数都nb死了

N=2442

还16个子带

kvco各带得有多大差异

控制电压还能来回变化这么大

严重的不稳定

你这原因可能很多种,但环路参数先给大家看一下吧

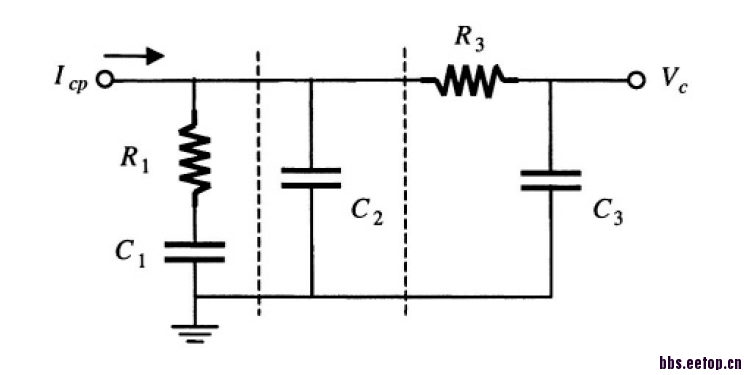

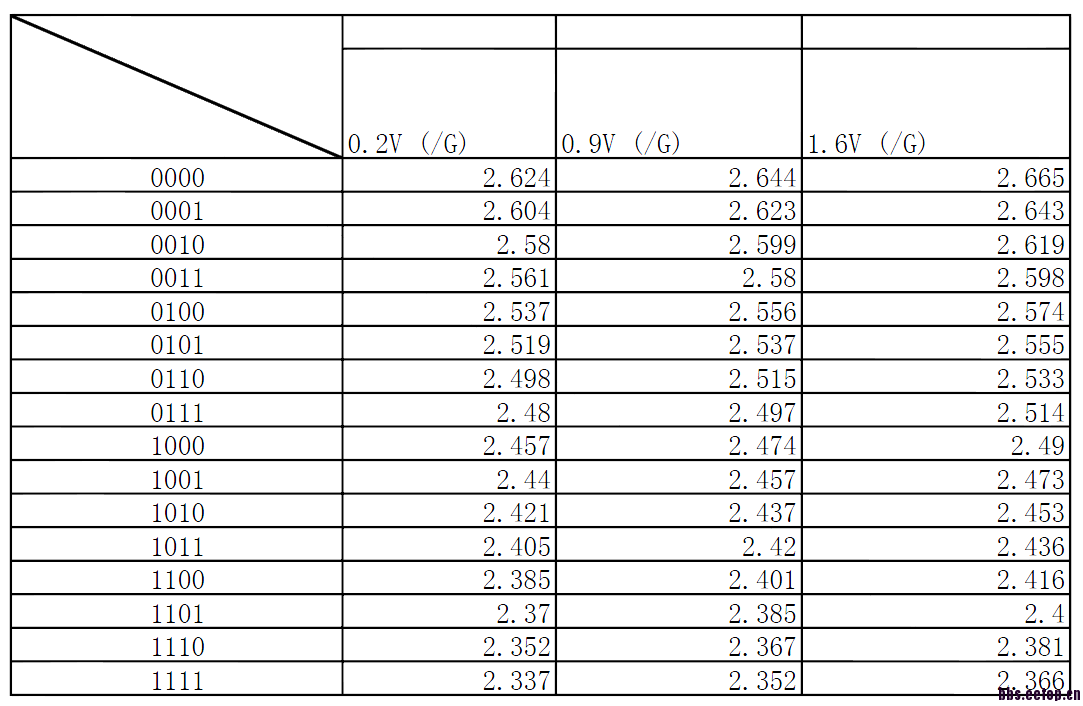

首先谢谢你们的回复!整个的PLL的架构如下图:参考频率是1M的,PFD用的是无死区的;电荷泵是用的自举结构电流为20.55uA; VCO 的增益kvco=23.57M/V; 分频器中的预分频部分用的是16/17分频,高速部分是用SCML结构跟8选1的选择器构成脉冲吞吐结构,低频部分是用数字做的,总的分频比为2442;滤波器用的是三阶无源滤波器,结构及参数也一并附上如下R1=2.9353M, C1=2.3722p, C2=0.10651P, R3=2.5943M, C3=87.141f:VCO的仿真数据也一并附上:

在混合仿真时已经选定到1010的子带,但是最终vco的控制电压却在0.2~1.6之间来回变化,没有锁定在2442的频率处,请各位大神多多指导,感激不尽!

N=2442

,延时你仿过没有?

有多大?

你这门还没入,别急着仿真,一个一个模块弄清楚。

你这个pll不稳定,看看相位裕量是多少

晕,你告诉我你这pll bw多少?

首先谢谢你的解答!BW=80k, 用matlab计算的相位裕量为54.5

期待您的回复,谢谢

首先感谢您的解答!

延时没有仿,我不知道是哪儿的延时,求指导,谢谢

分频比是2442,有个积累延时,太大以后,PFD就会有偏差,引入的jitter很大,导致不可用

请问下,这个延时应该怎么仿?

你是闹着玩么?R1=2.9353M, C1=2.3722p, C2=0.10651P, R3=2.5943M, C3=87.141f

这参数......,真让人无语...

这几个参数是根据Keliu Shu 的 <CMOS PLL Synthesizers Analysis and Design> 这本书用Matlab 计算出来的,如果有什么不对的地方恳请指正, 您是怎么确定LPF的各个参数的方便指导下吗?

谢谢!

R1,R3这么大 片内放得下么 C3又这么小,跟寄生电容的量相当...

R1 R3 这个片内能放得下,您说的C3确实有这个问题,您在做的时候是怎么确定各个电阻、电容参数的呢?

请问这个“积累延时”是怎样作用的?有相关paper可以参考吗?

光从参数来说,这个PLL系统bandwidth 大概80KHz,phasemargin 52deg的样子,是个稳定系统

但是实际做成电路,这个东西确不行

Icp=20uA,R1=3Mohm,Icp*R1=delta V=60V

最简单的想一想,在PLL没有lock时候,charge pump 电流会在Vctrl上形成一个几十V的跳动

你的电源电压也就1.8V,无法handle这个几十V的跳动

PLL 不能lock也是正常的咯

那么如果为了得到80k的带宽,LPF应该怎么计算?求指导,谢谢

LPF无能为力,PLL的参数和Icp,Kvco,N, LPF都有关系

怎么可能只动LPF就能meet requirement呢?

说实话,你这个design的最大问题就在于N 和 Kvco,不要照着书去搞,书上很多都是早扯淡

我是没见过2000多的分频比,中心频率2.4G Kvco 23MHz/V的VCO,不切实际啊

这个1MHz一个band的应用是2.4G的bluetooth,你是为了做整数分频,分频系数2440

实际大家都要做小数分频

感谢各位大神的耐心解答,在你们的启发下我重新设定了环路带宽,从80k降为10k,重新仿真了下,应该是锁住了,建立时间大概是150us左右。但是实际输出频率比想要的输出频率低了4M左右(想要输出2442M 实际仿真输出的是2438M);VCO经分频后输出信号的相位一直超前参考频率(参考频率1M)10ns左右。再请问上述这些问题是合理的误差还是电路本身就不对?

如果真的锁住了,应该频率精确相等,怀疑你测量出来的频率不是最终完全锁定后的频率值或者是测量误差。

谢谢您的回复:后来我将计算输出频率的时间段延长了些,发现这样计算出来的频率值更加接近想要的输出频率了。另外,如果锁住了的话,分频后的时钟的上升沿是不是与参考频率的上升沿完全对齐呢?

实际中可能看不到分频后的时钟的上升沿与参考频率的上升沿完全对齐的情况。其实phase锁定并不见得是phase相同,相位差一定,就可以认为是锁定。

fuyibin ygchen2

二位应该都是资深人士了。

晓得了,学习了,感谢万分

学习了,感谢万分

你可以去下一个PLL sim 去仿真一下。

电阻,电容的参数值太不协调了,很多资料提供一些比较普遍的算法,由相位裕度和环路方程推导出滤波器的参数,对于分频器,这个分频比带来的动态功耗非常大,而且多配合小数分频,个人愚见。哈哈

谢谢,请问您那儿有没有推导滤波器参数的相关资料,能不能分享下?