菜鸟请教大神HSPICE仿很短的verilog-a

时间:10-02

整理:3721RD

点击:

verilog-A程序如下://This model is used for testing, and it will be modified without notice.

//vp: positive terminal

//vn: negative terminal

//vr: node between resisitor and conductance

//vl: noed between conductance and capacitor

`include "disciplines.vams"

`include "constants.vams"

module fecap(vp,vn);

inout vp,vn;

electrical vp,vn,vr,vl;

//parameter declaration: name= value [unit]

parameterreal c=0.04369;

//[uc*v]

parameterreal a=0.7878;

//[v]

parameterreal vm=5;

//[v]maxmial voltage

parameterreal vc=1.5435;

//[v] coercive voltage

parameterreal Area=1E-3;

//[cm^2]

parameterreal A=96;

//[A/(cm^2*K^2)] Richardson constant of Si

parameterreal T=300;

//[K] room temperature

parameterreal phib=1;

//[v] potential barrier height

parameterreal e=1;

//[e] electron charge

parameterreal pi=3.14;

parameterreal e0=8.854e-15;

//[F/um] vacuum permittivity

parameterreal er=400;

//dielectric permittivity of PZT

parameterreal w=3e-1;

//[um] depletion layer thichkness

parameterreal k=8.61e-5;

//[eV/K] Boltzmann constant

parameterreal R=1;

//[ohm]

parameterreal L=1;

//[ph]

real ddv;

real q_cap;

//charge on capacitor

real id;

//current across a Schottky contact

real id0;

//reverse saruration current

analog begin

ddv=ddt(V(vp,vn));

if(ddv>=0)

q_cap=c/(2*a)*(atan((vm+vc)/a)-atan((vm-vc)/a))+c/a*atan((V(vl,vn)-vc)/a);//lower branch

else

q_cap=c/(2*a)*(atan((vm-vc)/a)-atan((vm+vc)/a))+c/a*atan((V(vl,vn)+vc)/a);//upper branch

id0=Area*A*T*T*exp(-e*(phib-sqrt(e*abs(V(vl,vn))/(4*pi*e0*er*w)))/(k*T));

id=id0*exp(e*V(vl,vn)/(k*T))*(1-exp(e*V(vl,vn)/(k*T)));

I(vp,vn)<+id+ddt(q_cap*1e-6);

V(vr,vl)<+ddt(L*1e-12*I(vp,vn));

V(vp,vr)<+R*I(vp,vn);

V(vp,vn)<+V(vp,vr)+V(vr,vl)+V(vl,vn);

end

endmodule

网表文件如下:

*file: fecap.sp fecap

setenv HSP_VACOMP_OPTIONS –G

setenv HSP_VACOMP_OPTIONS –B

.hdl fecap.va

vs p n 5

x1 p n fecap

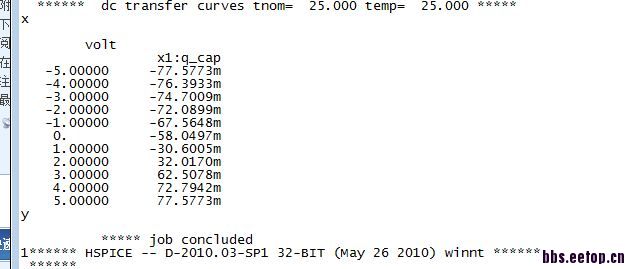

.dc vs -5 5 1

.plot x1:q_cap

.end

在HSPICE里面仿真,直接说setenv设置环境就错了,后面又说q_cap未知,请问怎样改网表呢?

有什么问题给我回信

//vp: positive terminal

//vn: negative terminal

//vr: node between resisitor and conductance

//vl: noed between conductance and capacitor

`include "disciplines.vams"

`include "constants.vams"

module fecap(vp,vn);

inout vp,vn;

electrical vp,vn,vr,vl;

//parameter declaration: name= value [unit]

parameterreal c=0.04369;

//[uc*v]

parameterreal a=0.7878;

//[v]

parameterreal vm=5;

//[v]maxmial voltage

parameterreal vc=1.5435;

//[v] coercive voltage

parameterreal Area=1E-3;

//[cm^2]

parameterreal A=96;

//[A/(cm^2*K^2)] Richardson constant of Si

parameterreal T=300;

//[K] room temperature

parameterreal phib=1;

//[v] potential barrier height

parameterreal e=1;

//[e] electron charge

parameterreal pi=3.14;

parameterreal e0=8.854e-15;

//[F/um] vacuum permittivity

parameterreal er=400;

//dielectric permittivity of PZT

parameterreal w=3e-1;

//[um] depletion layer thichkness

parameterreal k=8.61e-5;

//[eV/K] Boltzmann constant

parameterreal R=1;

//[ohm]

parameterreal L=1;

//[ph]

real ddv;

real q_cap;

//charge on capacitor

real id;

//current across a Schottky contact

real id0;

//reverse saruration current

analog begin

ddv=ddt(V(vp,vn));

if(ddv>=0)

q_cap=c/(2*a)*(atan((vm+vc)/a)-atan((vm-vc)/a))+c/a*atan((V(vl,vn)-vc)/a);//lower branch

else

q_cap=c/(2*a)*(atan((vm-vc)/a)-atan((vm+vc)/a))+c/a*atan((V(vl,vn)+vc)/a);//upper branch

id0=Area*A*T*T*exp(-e*(phib-sqrt(e*abs(V(vl,vn))/(4*pi*e0*er*w)))/(k*T));

id=id0*exp(e*V(vl,vn)/(k*T))*(1-exp(e*V(vl,vn)/(k*T)));

I(vp,vn)<+id+ddt(q_cap*1e-6);

V(vr,vl)<+ddt(L*1e-12*I(vp,vn));

V(vp,vr)<+R*I(vp,vn);

V(vp,vn)<+V(vp,vr)+V(vr,vl)+V(vl,vn);

end

endmodule

网表文件如下:

*file: fecap.sp fecap

setenv HSP_VACOMP_OPTIONS –G

setenv HSP_VACOMP_OPTIONS –B

.hdl fecap.va

vs p n 5

x1 p n fecap

.dc vs -5 5 1

.plot x1:q_cap

.end

在HSPICE里面仿真,直接说setenv设置环境就错了,后面又说q_cap未知,请问怎样改网表呢?

比较急,verilog-a程序没有问题,就是想把q_cap打印出来,用print和probe问题都一样……

有什么问题给我回信