数字模块前后仿真不一致

时间:10-02

整理:3721RD

点击:

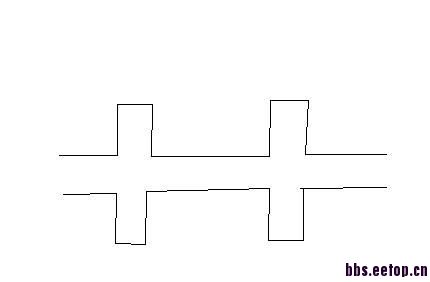

最近拿到反相出来的一个数字电路的版图(产生多相位时钟的),原理图也有,只是未经整理看起来非常乱,做LVS是通过的,但通过前后仿真发现,其中有几个端口产生的时钟相位恰好相反(如图,同一端口的前后仿真结果),请问这有可能是什么原因?还是第一次碰到LVS通过的情况下,前后仿真不一致。

脉冲间隔多长时间啊?会不会是因为LAYOUT延迟造成的

脉冲宽度约为20微妙吧,延迟怎么会造成反相,图中占空比为四分之一

有木有哪位碰到这个问题的?

已解决,port 与label不一致造成的!