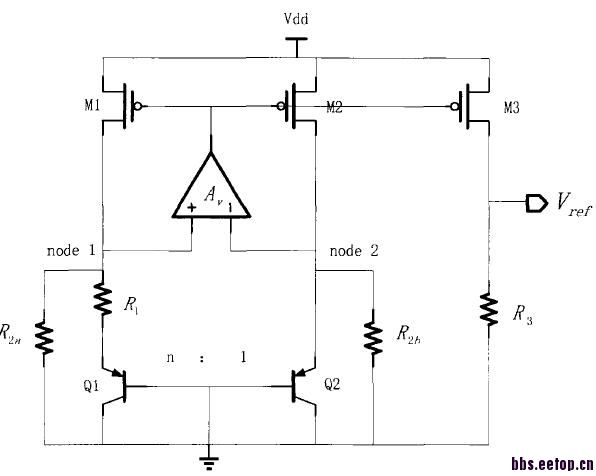

带隙基准PSR求助

差分对的bulk接源极不要接VDD

这个结构本身的PSR就难做的很好。

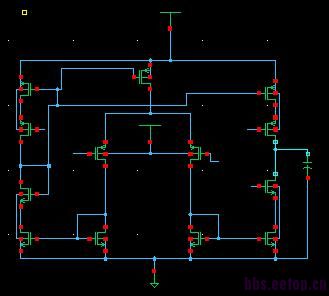

运放搭错了吧

你是说bandgap结构的问题吗?那哪一种的PSR能好点呢?还有这种结构的PSR极限能有多少?能赐教一下吗。

你看哪儿错了 能否指点一下 3Q

这种运放的PSR的确不高 近似为1 但是放在bandgap中就要利用这一点呀

看不明白左边的nmos连到输入管的尾电流源的栅极,是sansen书上的还是复旦那篇论文上的?

哦 那是自偏置

电路出处在哪里,不清楚为什么自偏置要接到输入管尾电流源的栅

偏置是有问题的。

我知道了啊,还来混积分

偏置出了什么问题,能告诉下,怎么改善的么?

真能扯淡。

1,你的运放里接的是二极管接法的负载,这种电路增益能达到70db?

2,除了增益,你的运放的工作点呢?失调电压呢?offset很大的话你的bandgap怎么可能工作?

3,我在做自偏置的时候发现启动电路的情况很大,如果可以不建议用这种结构。

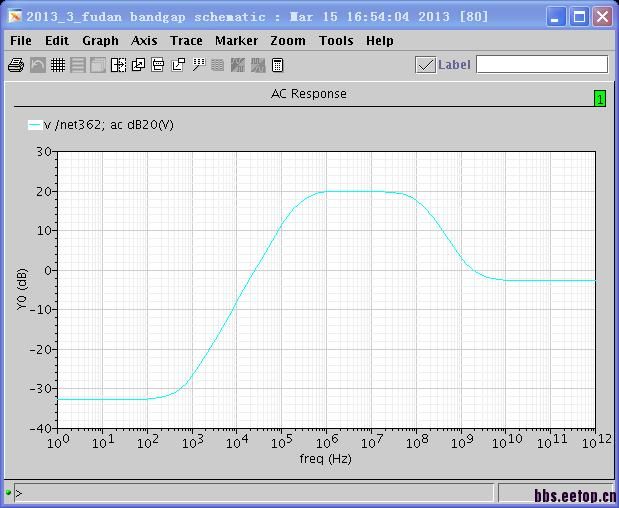

运放本身的PSR有仿过么?印象中,曾经仿过类似的bandgap电路,PSR也没这么差。应该跟运放的结构有关系。

对,运放工作点没有问题,增益也能达到,但是多次自偏置增加了过多的零极点,导致不稳定还有,自偏置的启动的确是个问题,后来改进了,采用简单的两级运放,但是带隙PSR有的部分为正,请问高频部分正的PSR是否有害?又该怎么改进呢 谢谢

呵呵不好意思是扯错了,你说的对整个环路增益和自偏置电路对psrr的影响是更大。

比较优秀的LDO的psrr参考值为10k时>60db。对于BANDGAP的要求会达到80db。高频会是正的很正常。但是你正的太多了就是有问题了。另外可以仿下时域,看下特定频率的纹波到底产生怎样的影响。

受教了,3Q。

差分对管衬底接源级,电流镜采用cascode

电流镜负载用cascade结构 我仿出来的 psrr差不多 低频是-87db 高频是 -30多 想问问你的那个运放是怎么设计的?

我后来换了两级的运放 原来那个运放由于自偏置太多 电源抑制能力很差 后来舍弃了

感觉运放接得有点问题啊