高压buck DC-DC流片后PASS管在上电过程中烧毁,请高手指点,谢谢!

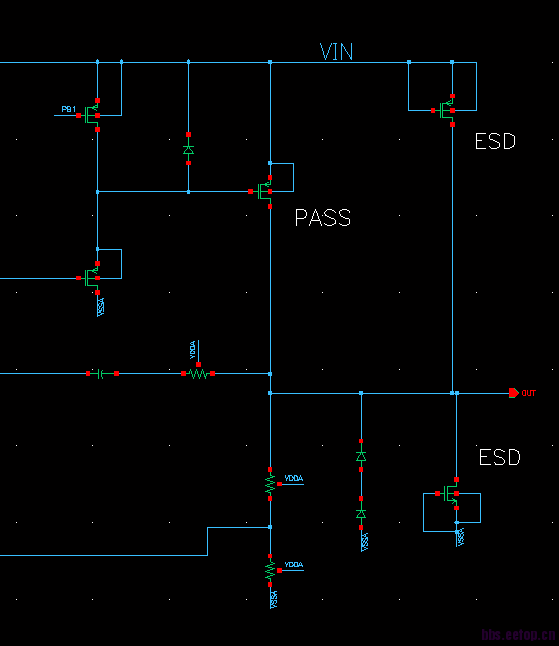

下图是芯片的模块图

设计输入为12-40V,输出为3.3V , 芯片里面集成一个VIN输入, 10V输出和外接2.2uF负载电容的的LDO,

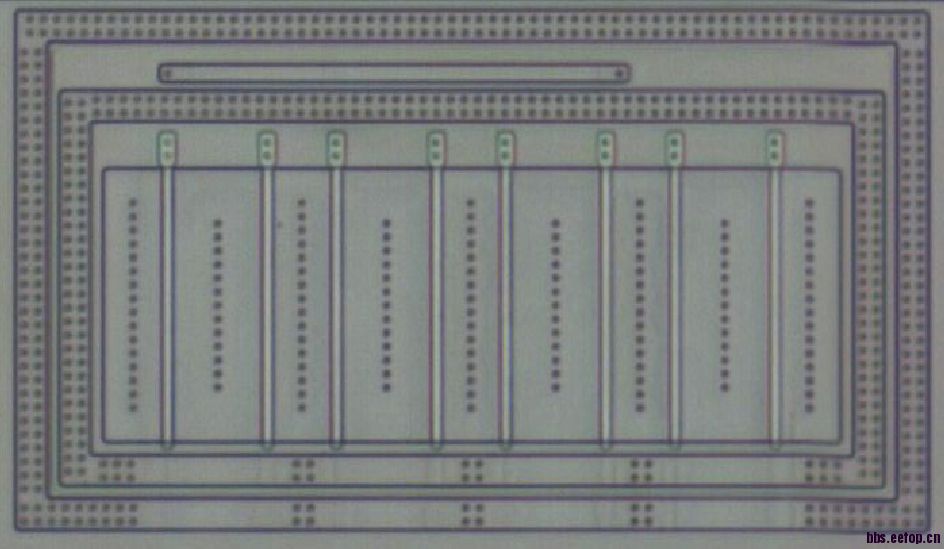

用的是高压管做PASS管,其特性为VGS能承受12V,VDS能承受40V,管子尺寸为150u/1u,如下图所示,图中

的二极管是6V的钳位二极管,这样就算在上电大信号过程中EA完全切换,PASS管的VGS不会超过6V。

这个BP10的PIN已经过了HBM 2kV的ESD。

上电时间约为1.5ms,工作环境是socket测试板。上电只能到20V芯片就损坏,经过拍照分析是芯片内部10V LDO的PASS管损坏,如图所示。

这个pass高压管直接连到芯片外面,是普通的版图,并不是下面的这种常见的ESD版图

LDO的pass管烧毁这可能是什么原因呢?请高手指点,谢谢!

看看VIN 和BP10的波形呢......

LDO20V IN

VO=10V

PMOS power = 10V *I ..

會不會 流過大電流

還有 vin 有無 spike? overshoot

還有 是否發生某些地方 latch up ?

block图中用的是NMOS

schematic中用PMOS ?

VIN20V时,VDS有10V,PASS管有60ohm左右?

电流大概要超150mA,孔打的够不,用没用Top thick metal,看版图上PASS管源漏没有大面积金属连啊,不道分析对不。

我有点没看懂,6V钳位二极管加上了,输出的调整范围够么?大负载

首先感谢大家的回复!

明天会仿真下相关电压和电流波形。上电后再过几ms,在VDD基本稳定不变后,用示波器看的确是有短时间很窄的上下尖峰,幅度是1,2V左右,随后会把这个波形发上来

这个芯片是替代国外同型号的,这个模块图是别的公司的,从spec看来这个regulator用的PASS管是NMOS。我们改成LDO了。

这个LDO输出的电流负载能力很小,也就70mA左右。

我猜人家用NMOS没有问题,你用PMOS就烧坏了。且是在上电时候烧坏的。

测试分析如下:

1.上电时间用斜坡缓慢上电,VIN=1V/S (很慢)看看是否还是发生此类现象。

2. 如果上述实验没有被烧坏,可以肯定的是,上电过程中你的PSSS device VGS太大。

3. 高压管子一般VDS可以耐很高的电压,你的VGS真的可以>10V吗?

4. latch up

"的二极管是6V的钳位二极管,这样就算在上电大信号过程中EA完全切换,PASS管的VGS不会超过6V。"

你的分析不对吧,这个diode不是保证VGS<6V的功能。如果VREF上电比较慢,你上电很快,VGS是可以很大的(VGS可以达到VIN)

钳位时,二极管电流会比较大,即使VREF=0,下面对VSS的PMOS应该没能力把二极管P拉到地吧

外接2.2uf电容,启动时如果power supply来的很快,来不及响应,pass pmos必须对2.2uf电容充电,这个过程pmos的vgs>12V,也许就break down了.

谢谢大家的回复! 试过了将软启动的SS/SD拉到零,这时候输出的驱动是关闭的,BP10的负载是芯片内的直流。

缓慢或者快速上电,能够到40V,没烧。再设Vin=18V ,SS/SD=0 , 输出的驱动关闭,给BP10负载一个外接到地的300mA的电流,随着时间过去,10V的LDO电压会慢慢的往上飘,速度大概是0.2V/S高到一定程度后芯片就烧毁了,但如果在上漂的过程中关掉负载,芯片还是好的。试了两个板子和芯片都这样,真是很奇怪啊!

由于有钳位二极管,VGS最大也就6V

不太理解。

个人分析:

1).从FA照片上看,顶层金属烧毁的痕迹不是特别明显,貌似底层管子被烧黑了。从这个角度看,不是顶层金属电流密度不够而造成的,如果是金属电流密度不够,也就是说金属线宽不够,那么顶层金属烧毁以后变黑并且造成短路。

2).排除1)的可能性,那就属于PMOS功率管的问题了。其一,考虑Latchup。上电时候功率管对负载充电,当遇到阻性负载时候,过冲比较大。这个过冲电压的抬高是造成Latchup的一个原因之一。建议:1.给AGND串联一个1欧姆电阻,分析瞬态过程,看AGND被抬高多少毫伏,如果超过一个PN结导通电压,请注意大电流的出处!2.给LDO加限流保护,本人也遇到过Ti的一个芯片,内部LDO没有限流保护但是Ti没事,咱们就挂了!3.NMOS做为PASS管,不会造成严重过冲,毕竟Gate电压上电过程需要CP慢慢抬升电压,或者靠EA提供Driver Voltage。而PMOS的Gate Voltage 靠EA控制,EA存在摆率限制,很可能动几下,然后PASS管输出电流就冲几下,接着就挂掉。

3).具体分析PASS管烧毁部分,到底是Gate打穿还是沟道打穿?是否考虑PASS管的L取值问题?考虑具体工艺,例如punch through 之类的效应是否考虑.L不要取太小,一味追求Low Dropout 对可靠性是一种藐视。

谢谢你的热心指点!

烧坏的原因可能有两个:

1. 钳位的zener管没有将VGS钳住。

2. 在pass transistor上面的功耗过大,导致温度过高,烧坏。

先说原因2:

2.1 看你给出的功能框图,里面设计了over temperature protection (OTP), 不知道实际的电路是否在过温的时候将LDO也关闭。

如果过温将LDO关闭,那么在上面0.2V/s的速度这个量级,芯片里面温度肯定是来得及传递的,OTP可以可靠的关断LDO,pass transistor不会被烧坏。可以排除原因2.

2.2 如果OTP发生没有将LDO关断,那可以在VIN缓慢上电,LDO带负载电流的情况下,测试在烧坏之前是否发生了OTP。也许下面这个测试方法可以: SS正常,将FB拉低,用10kohm的电阻将LDRV 上拉到5V。VIN缓慢上点,LDO带一定负载电流,OTP没发生之前,LDRV上拉到高电平,OTP发生后,LDRV被下拉到低电平(不知道你芯片的逻辑是否在OTP时也把LDRV关掉,如果关掉,这个测试方法就不行了)。

这个测试,如果在烧坏之前没有发生OTP,那肯定不是原因2,基本上是原因1了。

如果在烧坏之前发生了OTP,那基本上就是原因2了。

对于原因1:

从你的描述来看,LDO的VGS被钳位时,最大的输出电流能力为70mA,根据你给的pass transistor尺寸,150u/1u (看起来你的版图尺寸要比这个比例大得多?),VGS钳位6V,估算也在50mA左右。

但是你之前的测试,在LDO负载上面加了300mA的负载电流,LDO的输出电压没有被拉到地,还是可以上升。这表明pass transistor的VGS没有钳位在6V,可能已经大于10V了。从这个测试来看,说明zener管没有起到钳位作用。 但这也只是说明可能是原因1,不能排除潜在的原因2。

这个嵌位电路太冒险了,应该用高压bjt管连成二极管方式,接在嵌位的diode管下面,如果电压超过12v,让此嵌位电路导通,使得LDO的PASS管的栅极电压小于12V

标个记号,以后再看

学习了

谢谢

学习了

latchup 可能性较高。

小编这个最后是什么问题?成功解决了把?