请教一个LDO的上电延迟问题!

时间:10-02

整理:3721RD

点击:

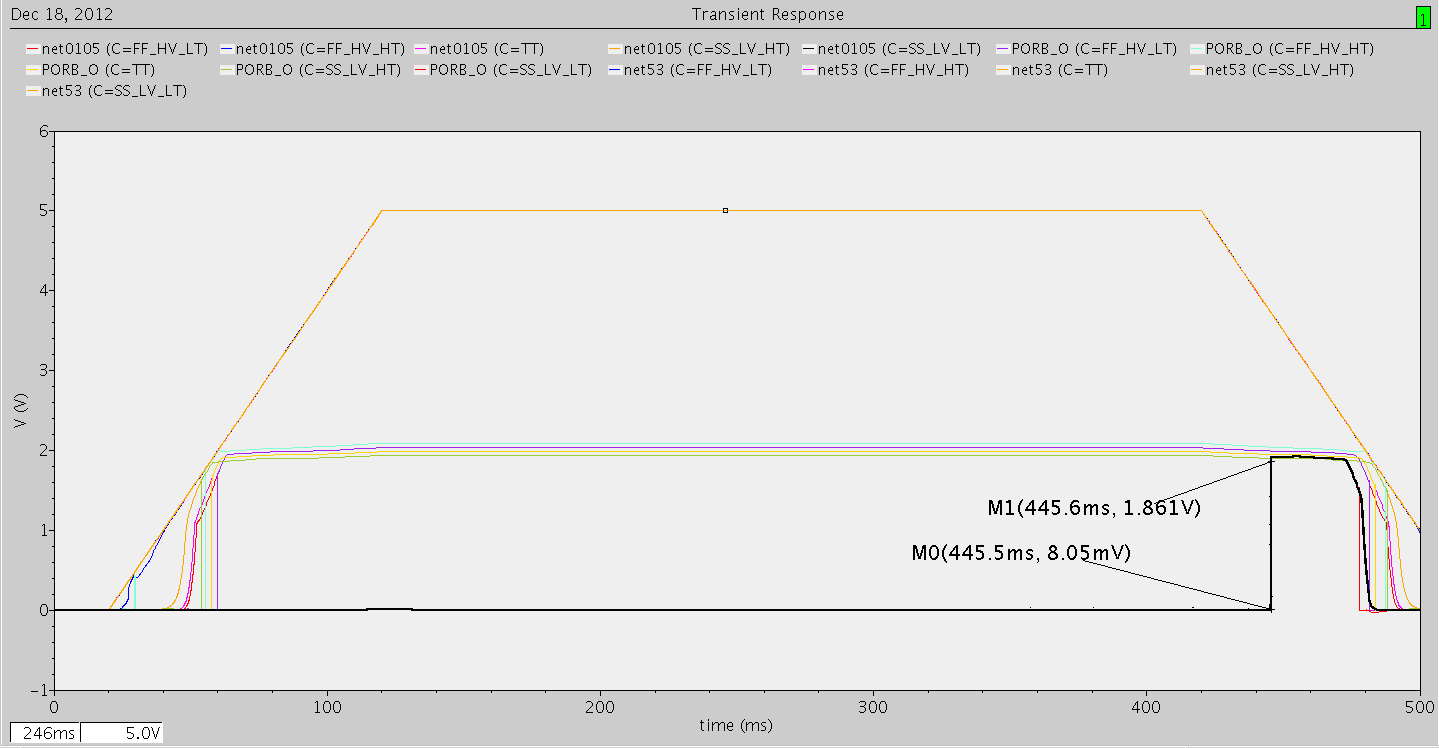

RT,图为输入电压5V,温度为LT-40 HT120跑的,在SS_LV_LT 的corner下的仿真(此时LV也是给的5V)。能看出有一个明显的延迟。小弟目前推测是驱动能力太差。然后就增加了passelement的W/L。在输入电压为5V 6V时,没有该问题,但跑输入电压为4V的corner时,即SS_LV_LT -40 4V 的情况,

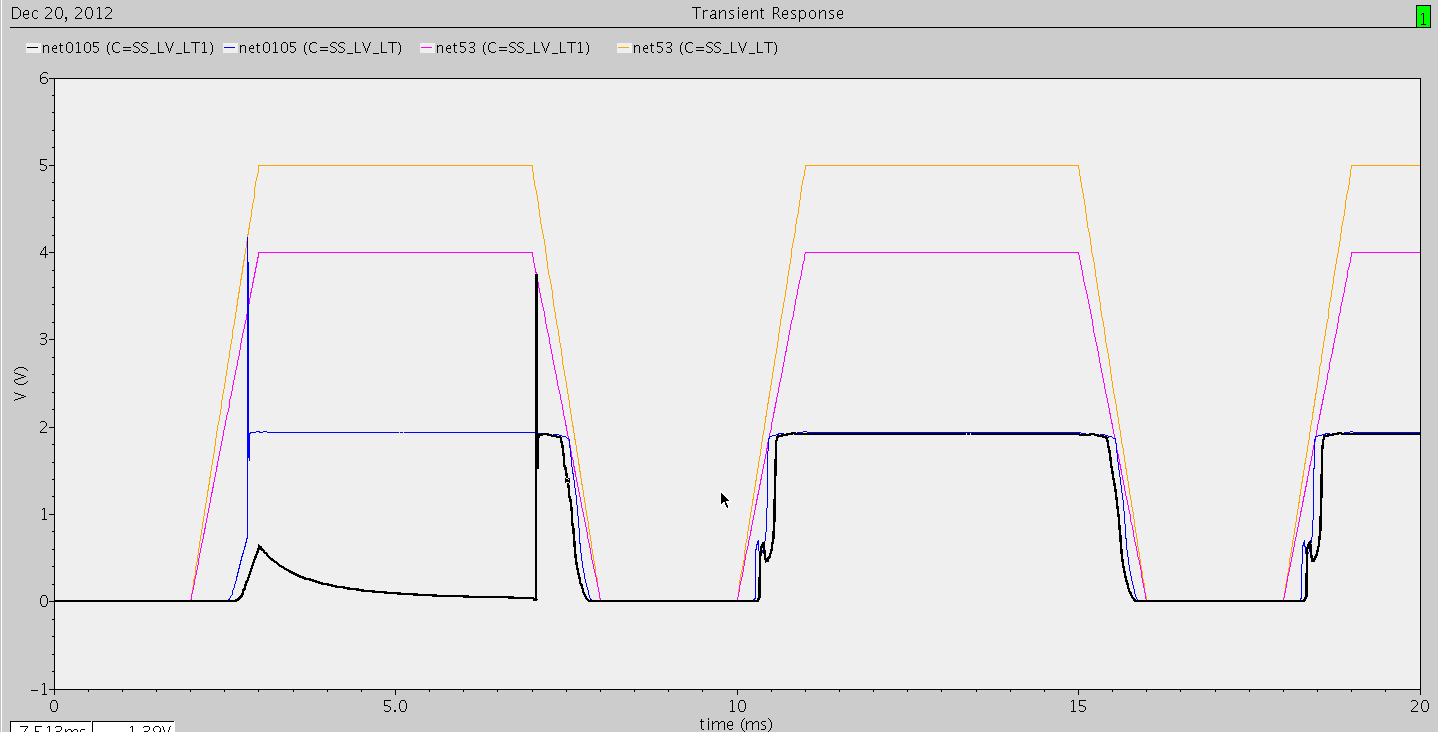

RT,图为输入电压5V,温度为LT-40 HT120跑的,在SS_LV_LT 的corner下的仿真(此时LV也是给的5V)。能看出有一个明显的延迟。小弟目前推测是驱动能力太差。然后就增加了passelement的W/L。在输入电压为5V 6V时,没有该问题,但跑输入电压为4V的corner时,即SS_LV_LT -40 4V 的情况, ,图为改过后。又复现了该问题。求大牛给点意见!

,图为改过后。又复现了该问题。求大牛给点意见!

你看一下基准上电

猜测是启动问题

你能不能帮忙把以下几个关键点给Plot出来:

1. Vin, 请让Vin的上升时间,控制在1us时间

2. Band Gap输出电压

3. 内部的UVLO信号

4. 输出大Device的Vgs信号

5. 输出电压

尽可能让你的Vin持续时间久一些,只Plot关键的时间段。

如果你的上升时间和Vin关系比较大,那么需要重点关注一下你的Error Amp.在驱动输出Device是否足够。其实说白了,你的整个环路最终完成的就是给输出电容充电,就是你的整个环路的摆率和哪些关键位置相关,就检查哪些地方。

我还是最怀疑你的Error Amp.设计的有些问题,看看这个模块是不是电路配置出了问题。

非常感谢各位的回答,此现象只发生在输入电压上升时间很慢的情况下。在减小负载时,能重新使结果变好,貌似确实与驱动能力有关,因为只跑了常见corner,仍然不能确认该问题发生的原因。

想请问下各位大牛,一般查错或者说在cadence上还原dip测试结果的方法是什么呢?mont carlo?corner?