如何理解共源共栅结构有助于改善电源抑制

时间:10-02

整理:3721RD

点击:

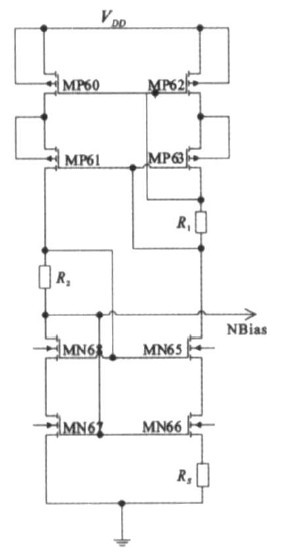

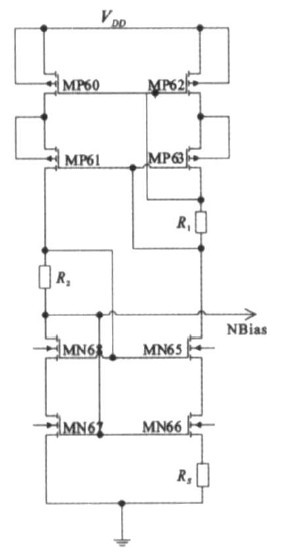

关于共源共栅结构可以改善电源抑制 大家是如何理解的?

比如以下这种结构是如何改善电源抑制的

比如以下这种结构是如何改善电源抑制的

M64漏看到下面的电阻1/gm,上面的电阻因为cascode增大了,所以vdd的psr变好了,vss的psr从右边那路看类似

分析的有道理,不过psr为什么只从一边看呢,不是应该两边要同时考虑吗?

嗯,是都要考虑的,比如在直观看vdd 的psr时右侧的一路中,M63漏端向上的电阻本身就很小(1/gm),这使得vdd上的噪声几乎都能在M63漏端出现,你可以计算一下这时右侧这一路尽管下面NMOS增加了cascode但是这一路的出现在M63漏端的电源噪声和不加cascode时相比约为1,换句话说右侧这一路的cascode并没有让M63漏端的电源噪声增加;而左侧PMOS增加的cascode却让出现在M64漏端的电源噪声比不增加cascode时小了约gm*ro倍。vss的psr也类似。

这些都是直观上的看低频的psr,实际上关注一下电源上可能出现的噪声频率范围比关注低频的psr更有意义,cascode的加入也会让psr的极点更加的低频。

为了得出更加精确的关系,小信号的模型肯定是最好的了。

楼上几位已经解释的很详细了。就不多言了。

谢谢你,你分析的很好,只是有一点我不太明白,就是M63漏端的噪声加入cascode和不加cascode时相比差不多,而M64漏端的噪声加与不加cascode却发生了很大的变化,左右两支路的情况是类似的呀,怎么会有这么大的差别呢?

真心来学习来了