急问:PFD可以消除周期滑步现象吗?

时间:10-02

整理:3721RD

点击:

觉得如果PLL中用了PFD做鉴相器,就不会出现周期滑步了。因为周期滑步是因为相差超出了鉴相器的鉴相范围,导致检相器朝相反的方向“纠正”频差,但在PFD中鉴频鉴相器没有鉴相范围的约束,所以不会有周期滑步现象,不知道对不对?

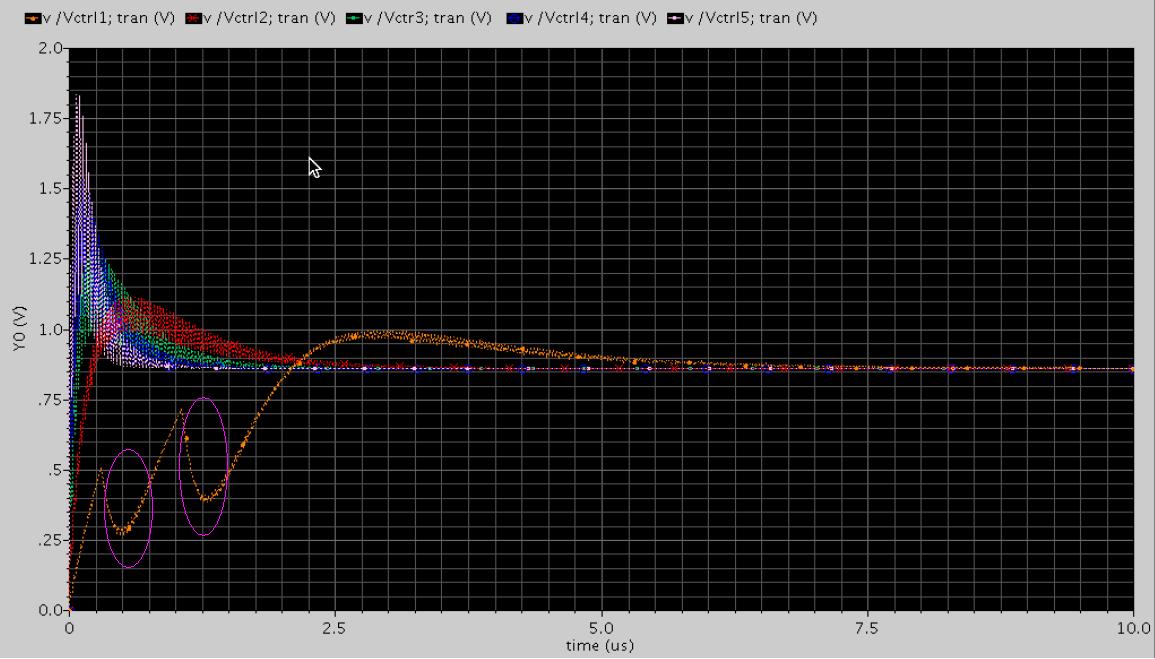

如果频率差比较大,用一般常用的PFD,在多数情况都会看到,在PLL初次锁定时看到控制电压边”振荡“边向目标电压靠近,一般就是这个现象引起的。

你指的周期滑步是不是图中黄色的那条控制电压线波形所描述的现象?我一直对这个过程不太明白:从那条控制电压线可以看出,分频后的时钟相位是落后于参考时钟的,所以控制电压才会往上升,但是在这上升的过程中,为什么电压控制线会有一小段“下降”,然后再一小段上升呢?(图中用粉色圈圈圈出来的过程),因为电压控制线有往下降的这一段,就说明PFD有一段时间是想把分频后的时钟相位往“相反方向”拉,这个相反方向会让参考时钟和分频后时钟相位差变大。但我无法理解为什么会有这个过程?我觉得应该一直上升,因为PFD的输出极性是不会出现让相位差越来越大的趋势的。

不太清楚那些vctrl在实际电路的具体位置,但看起来理解象是对的。当相位能够在滑移前被回路校正过来,滑移现象一般就不会再出现了。大概和回路行为和初始信号差有关系。

我也觉得是和初始相位差有关

有计数器型的PFD可以消除cycle clipping的现象,小编可以去看看。