有关采样保持电路建立时间不够的问题。

主运放(不带增益自举运放)仿真时,相伴达到77.78度,带宽612M,加入增益自举运放后,整个运放的带宽变为677M,相位变成了68度。(在信号通路上的增益自举运放,单独仿真的时候带宽为730M,略大于了主运放612M的带宽,它的负载电容以接入主运放点的寄生电容(大约为0.35p)为标准的。但是把它的接入到主运放中,整个运放带宽有扩展的现象,因此,当把增益自举运放加入到主运放后,在增益自举运放后再接了一个0.2p的电容,最后带宽才达到677M)。

把运放接到采样保持电路后,输入为1V的差分信号,它在5ns内达到所要求的建立精度(999.75mv)以上。输出如下图所示。

在输出波形图中,它过了第二个最低后,才达到精度。

本人发现有人说,他们在过了第一个最低点后,就可以达到所要求的精度。

本人想问一下,有没有可能过了第一个最低点后,就可以达到所要求的精度,以及怎么去做,是相位做得不好,以致于第一个过冲点过大,还是问题出在那里?

把运放接到采样保持电路后,输入为1V的差分信号,它在5ns内达不到所要求的建立精度(999.75mv)以上。达到所要求的精度可能要5.6ns.

貌似你的运算放大器的相位裕度太小了,出现了oscil

想问一下你的运算进行Phase_Gain仿真的时候用怎么样子的电路结构?设置了输入的DC工作点没有?

几乎可以肯定的是PM不够

PM,已经达到68了。

提高运放的带宽及运放的PM,就可以使运放在5ns内建立,还可以消除振铃。

小编什么样的采样保持结构?flip-around or charge redistribution?

你看的应该只是开环的带宽,或许由于你的输入管的(Cgs+Cgd+Cgd)而导致你的实际带宽不够了,就会那样

27

采用的是flip-around 型,仿真的是开环带宽,但是在算运放最低要求带宽的时候,已经考虑了反馈因子。反馈因子肯定大于0.5,小于1。

在保持时候的开关采用CMOS开关的,把CMOS开关的宽长比取很大(大约Wn/Wp=20/65,沟道长度取最小0.35)的时候,不会出现上面这种情况。但是CMOS开关宽长比太大了,会带来很多其它效应。肯定会使信噪比下降的。

The op-amp is poorly designed!

sw size你是可以做整体的fft分析来优化的,你的采样速度和精度要求都比较高,sw size肯定不会太少?你是0.35um的?这个process可能不太容易达到你的要求。0.18um应该比较容易一点呀。

小编说得非常正确。

在0.35工艺下,要达到所要求的精度和速度,是有点困难的。因为采样保持电路后接了一个大电容(8PF)。要提高运放的带宽非常困难(因为提高它的带宽的话,输入管子寄生电容也会增加。在负载电容(8PF)比较大的情况大,寄生电容增加的速度远远大于带宽的增长速度)。

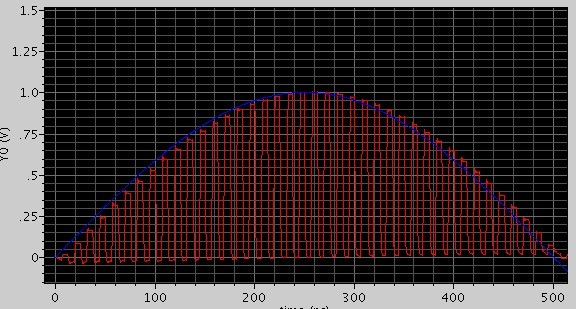

本人现在把采样速度降到80MHz,再把运放的带宽降低到了540M,整个运放(不加补偿电容的情况下)相位达到72度。性能好了很多。

输出波形如下:但是怎么会出现一个延迟?就是有点不同步的感觉,怎么会出现这种情况?

your sample cap is too big,no need so big value.usually 2p~4p should be ok. you can careful calculate this value.

我的采样电容取4.8P。因为是12位的。因为第一级MDAC是采用3.5级结构的。所以总的负载电容比较大。

想请教一下,折叠式增强型OP的共模反馈点放在哪比较好啊,是用哪种反馈啊

用开关共模反馈好一点,放在套筒结构的尾电流源上

为什么会产生延迟,怎么解决呢,还有那个建立时间的问题那位大侠能解释下,小弟也遇到了同样的问题

10# zhfhit 是应该采用更好的工艺

我们现在做12bit 200M 是用IBM 0.12

ADC也蛮有意思的啊

我也遇到了延迟问题,但对SFDR影响不大。还有你的电容这么大,能不能将理论4.8p的采样电容等效为小的采样电容+后面管子的寄生电容之和呢

学习,学习。

减小PM试试

个人经验是settling time不光跟GBW,PM有关,还跟non-dominant pole 和zero有关

如果你能够改变non-dominant pole的位置,可以试试