折叠共源共栅 增益自举运放 自举运放 环路带宽

时间:10-02

整理:3721RD

点击:

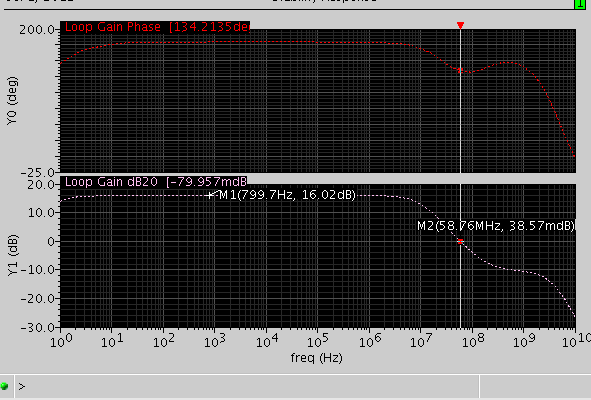

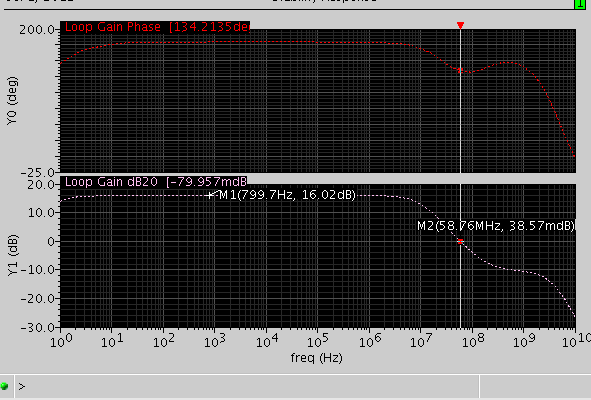

论文里说增益自举的运放的环路带宽要大于主运放的环路带宽,小于主运放的非主极点。

但是自举运放的环路带宽怎么仿的?

在通路上加一个stb,仿出来的结果差很多啊?

设计是增益自举的运放,gm=3.2ms,负载管子的Cgs=100f

结果环路放出来,GBW=50M左右,增益也只有16dB

是不是仿真方法的错误?各位做过这种运放的自举子运放的的带宽是怎么仿的?

但是自举运放的环路带宽怎么仿的?

在通路上加一个stb,仿出来的结果差很多啊?

设计是增益自举的运放,gm=3.2ms,负载管子的Cgs=100f

结果环路放出来,GBW=50M左右,增益也只有16dB

是不是仿真方法的错误?各位做过这种运放的自举子运放的的带宽是怎么仿的?

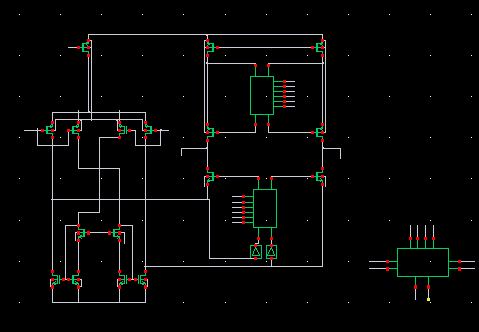

还是用的Recycling folded cascode