请问一下,如何设计一个输出电压为电源电压的一半!

难点:输出电压随电源电压而变化,并要求能尽量减小纹波的影响。

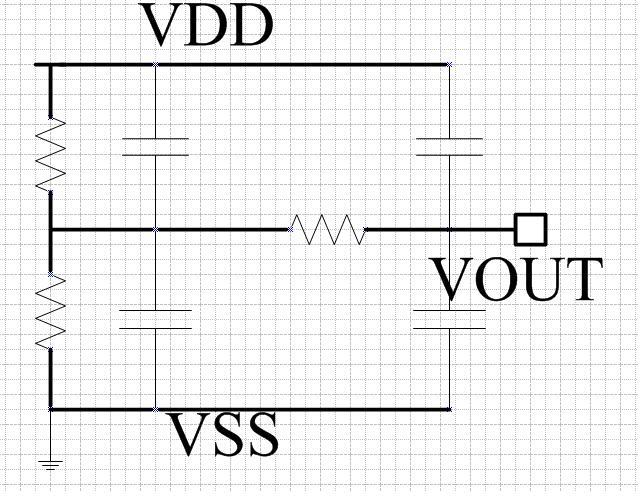

电阻分压,外挂滤波电容

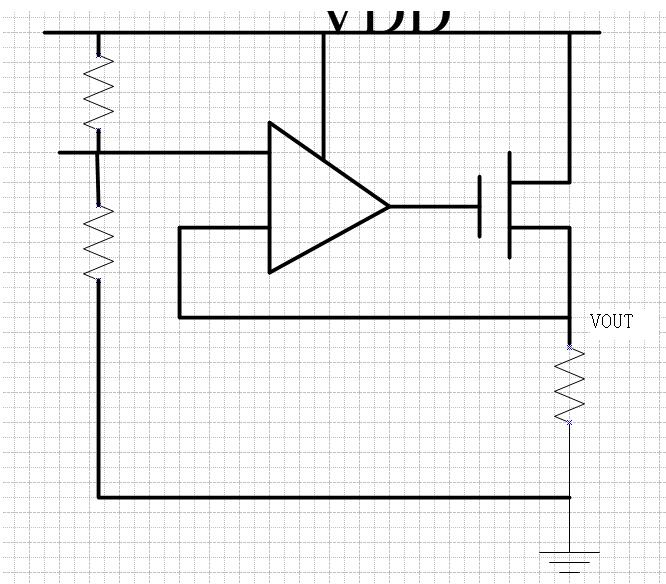

OpAmp + 源随器, OpAmp的正输入为电源的电阻分压,负输入为源随器的输出!

电阻分压,外挂滤波电容,滤掉高频

3L的不还是把电源地杂讯引进来了?

OpAmp可以滤波啊!呵呵

你不是电阻分压接到运放输入端了吗?这不是把电源地噪声直接传到输出了?

而且还是高频,直接从cgs过去

电源和地都有噪声,这个就比较麻烦了!

呵呵 同感

采用差模信号,去处噪声后才将输出电压

我有这样子去做滤波,但是没有效果,只有衰减6dB,也就是说只有电阻分压的作用

但是power 和ground都很脏,像这样连接,噪声仍然直接到达Vout

您所指的能具体点吗,怎样去除差模?

小编要的这个干净电压是最终目的吗

学习了

··

电源有噪声好说,大电容对地,等于vdd有一个低通滤波效果,或者多一个opa的buffer,这都是常用的。

至于地有噪声,我觉得是你没表达清楚。地是所有单端信号的参考点,对单端信号它就无所谓有噪声或者无噪声。除非你特别说明输出是差分信号或者电路中有多个地,需要细致考虑多个地之间的差异。那时候这个地其实也不是什么地,而是另一种信号。

这么多回复中,我要称赞16楼,gaojun927 对地噪声所作的那段叙述完全正确!对“地”没有真正理解的人是写不出来的。

做comparator的比较电压

这里的地明确来说应当看作是一个信号。

主要是因为pakage中有RLC,ground上有大电流变化,所以到芯片内部ground也会有glitch。

我猜测你考虑的是芯片地和系统地的差异?然后不幸的是系统中还有高速或者大电流信号?这个电阻分压结构里最主要的其实是那个电容,电容的地接哪里,就意味着高频信号以谁为参考,所以如果要以片内地为参考,一个主要问题是没有大电容可以用。我曾经看到jssc上有人用接近截止区的mos做大电阻进行进一步滤波,不过怀疑在实际中的效果,不太敢用。所以我觉得比较可靠的方法应该还是在系统级再想想办法,看是不是能电源地在芯片内分开,芯片外再单点连接。

过奖了,理论到实践还是有不少距离的。我经常在实践中碰到没法解释的现象,上周就有。

您说得很正确,正是由于高速大电流导致芯片地和系统地有差异,从而使得内部ground会很脏,所以不太好做滤波。您还能找到那篇JSSC相关的文章吗?