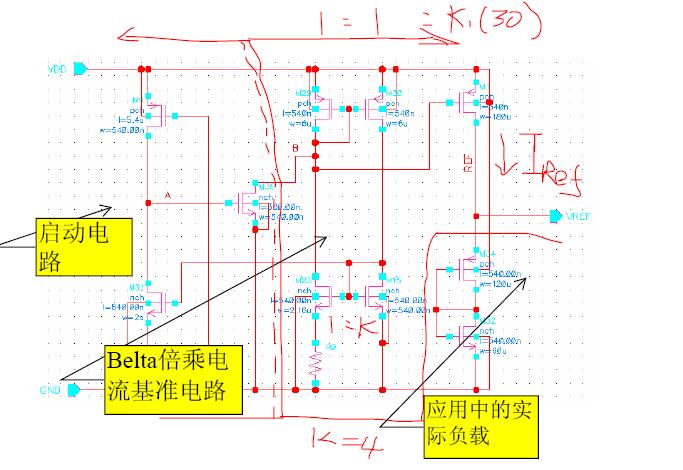

belta倍乘电流基准WL手算和仿真差异巨大,附电路和仿真图,你怎么处理这个经典电路?

这个电路在拉扎维和baker的教材里面都有。现在设计中需要利用。电流目标是5毫安。可是仿真结果却不到400微安。

附上电路 请大侠们不吝赐教。

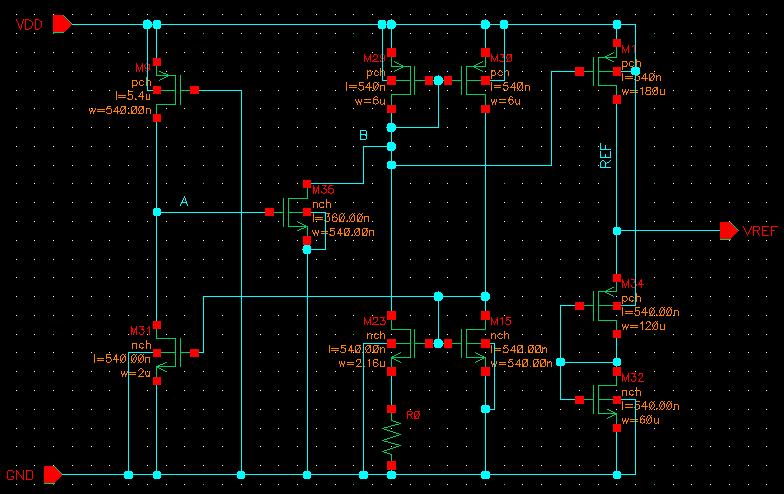

换张清晰的图

计算完全照书上的公式进行。估算参数

0.18um工艺UnCox=162UpCox=55Vthno=0.475Vthpo=-0.449

电流源上面三个PMOS W/L1:1:k1=1:1:30

下面2个NMOS W/L1:K=1:4

目标电流:Iref=5 mA

可是仿真结果却是390uA

请大家指点指点

也检查了工作点

是不是正常工作后,图中A点的电压还不够低?

各点电压都标详细些吧

所有管子都正常工作吗?

你的负载电流这么大,而你的电流源的L太小了,这就意味着你电流源的输出阻抗会很小。这么小的输出阻抗的电流源输出电流当然和你用假设无穷大的输出阻抗计算的结果有较大差异了。

你可以尝试增大电流镜pmos的L,同时利用负反馈钳住电流计的drain电压来增大输出阻抗

这里是0.18 um工艺,所以我最小长度去3倍最小长度(180nm),也就是540nm,这个长度也不够吗?

如果继续加大这个长度,按照belta倍乘公式将会发现右上角的输出管W/L比会非常大,有些担心这个巨大的WL比值。

你提到了输出阻抗问题,确实很有启发。谢谢大侠!

A点启动后的电压只有几十毫伏,应该是满足的。

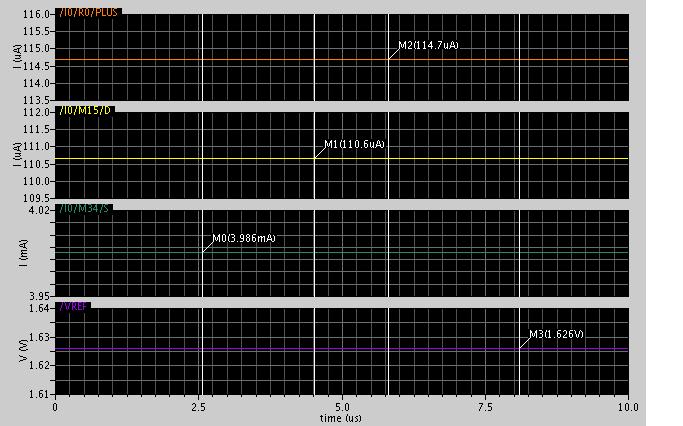

麻烦你贴一下 你中间的那两个MOS管子电流 和输出那一点REF的电压值看看

启动电路有待完善

按照前面朋友的启迪,加大了MOS的长度。

中间的那两个MOS管子电流 和输出那一点REF的电压值如图

各个管子WL参数

0.18uM工艺 1.8伏特供电

注意电流源的右上角PMOS参数达到2800um/4um(即 20* 140um/4um ) 相当大的参数才使得输出电流勉强到了4毫安,还是没有5毫安。

我感觉可能是你输出点VREF电压不够低你以前仿真到390U的时候 M0的工作点出问题了, 也许进入线性区了

作为负载的那两个MOS管在5MA的输出电流下 可能会把VREF电压抬的很高, 你可以修改下它们的W/L试试

谢谢 将负载管做得相当大,终于达到了5MA。

最大的MOS达到 40*140u/4u 这么大的管子,行么?

你都是怎么看是不是够了啊

弱弱的问下 你这个电路是作为电流偏置用 还是什么用 怎么要那么大的电流

做VCO的电流源

弱问,这个5mA是参考电流还是实际偏置电流?看似参考电流,但是有必要用这么大的参考电流吗?

计算有问题的

你做的电路不make sense,

按照你的比例

1:1: 30

167uA : 167uA : 5mA

167uA过 2u/2u的M15? 你搞错没有啊

算算R上的电压降,167uA * 4.3K=0.72V, M23、M15的Vgs差0.7V好像不合理

一般也就0.2~0.3V吧,所以把电阻取小,大管子取大

还有一个,不要取出这么奇怪的尺寸和值,电流就出10uA/25uA/50uA/100uA这样的整数咯

小编负载部分电路没有问题吗?要那么大的w/l?

输出电流的大小由右上角PMOS管的W/L决定,是增加W,而不是增大L!

是参考电流,我是想通过这样来减小VCO实际的NMOS偏置电流管子的尺寸,来减小对相位噪声的影响,不知道对否i?

你的分析和建议很有道理,我已经重新计算了。

由于输出要5毫安,所以输出管子的WL都要很大,则电流源的PMOS管子L也不能太小,以形成电流的镜像比。也就是1:1: 30必须是同一个长度下进行的。

run 一下transient,看是不是没有启动,还有就是L最好放到1u以上吧

L值太小了吧,L的大小是看性能要求来定的。

手算和Sim本身是由区别的,需要一个逐步改进的过程。

麻烦你贴一下 你中间的那两个MOS管子电流 和输出那一点REF的电压值看看

VCO的尾电流源可以通过在G极上加RC滤波滤掉,你这个电流源的温度系数是很差的,在Ss下会严重影响VCO的工作。

18#说得很对,你回去好好算算再仿真吧,先把启动电路去掉,仿好了电流源再加上,负载先用电阻代替好了。