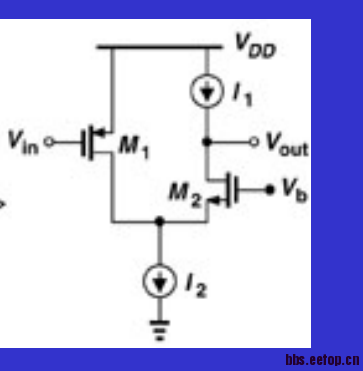

求问一个共源共栅电路

上图是一个折叠式共源共栅电路,拉扎维的书上讲,如果Vin>Vdd-|Vth1|此时M1截止(这个我理解),如果Vin<Vdd-|Vth1| M1导通且处于饱和区,这个饱和区是怎么判断出来的?电流源上方那个节点的电位不大好确定。

我上面的结论摘自拉扎维模电中文版76页。求各位大牛指点一二。

这只是个假设,折叠点的电压大于下面电流源的过驱动电压就行,所以输入管的Vds是比较大的

当Vin继续减小,以至于Id1=I1此时Id2=0,那么继续减小Vin,M1会进入线性区以使Id1=I1,为什么会进入线性区?这是怎么判断出来的?很多情况下这种不定量、定性的分析对我这中初学者来讲十分困难。

你也可以这样看,Vin减小后,M1的电流驱动能力越来越大,当他的电流驱动能力超过I2后,他就必须进入线性区了以减弱其电流驱动能力

哇,仔细一看回复我的是小编!多谢小编指点!

再问一句哈,你说的“需要进入线性区以减小电流驱动能力”,我的理解是:进入线性区后,Vds也对Id产生作用,因此,虽然Vgs使Id增大,但是Vds使Id减小,最终Id=I1。并非线性区的电流驱动能力就一定比饱和区小,对吧?

恩

你有没发现,Pro. Razavi书后面经常有很多画图的题,他强调的其实是:这种大信号的分析,用动态的观念来看比较清晰。例如这个问题,你要动态地看,Vin从很大的值Vdd开始缓慢下降。(缓慢的意思就是电路有充分的时间建立各个节点的稳定工作点)那么Vin很大导致M1的Vgs不足以导通,下降到某个值,即Vdd-|Vth1|时,M1会开始导通,这个时候必然是先经历sat,因为Vin还相对比较大,drain端不能建立反型层,即沟道夹断。只有等Vin降得更多(VDG够大)以至于夹断的沟道恢复了,此时进入triode region。所以书上的所谓“如果Vin<Vdd-|Vth1| M1导通且处于饱和区”是指它Vin是比Vdd-|Vth1| 小,但是没有小很多很多的时候。了解?要是Vin=0了,上帝也不能让M1进入sat region嘛,呵呵