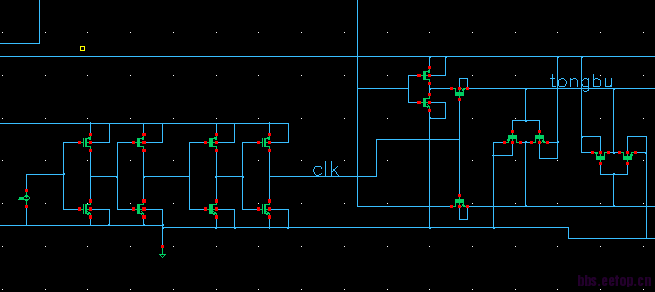

DAC中的时钟驱动电路的设计

时间:10-02

整理:3721RD

点击:

大家有谁做过DAC吗,这个DAC中的时钟驱动电路是怎么设计的。看了一些论文:时钟驱动电路能帮助信号同步,提高驱动能力(因为寄生电容等因素),减小上升和下降时间。但是,对它的作用一直不明白,时钟驱动电路加在mos管的栅极上,它是怎么样提高驱动能力的。时钟驱动电路是有一系列的反相器组成的。

谢谢大家的回复和解答

谢谢大家的回复和解答

在逻辑电路里面,有一个所谓fanout of 4,就是说每级输出时接到的下一级电路最优化时是上此级逻辑的4倍,所以比如说你有一个X1的inverter,就不能直接接去一个X1600的inverter,最好是X1->X4->X16->...->X1600,这过程就是你所说的驱动电路咯,不然的话直接驱动,上升下降都会很慢,还会导致延时。

还是有点不明白,你说的意思是:不同宽长比的反相器的连接吗,低倍宽长比驱动高倍宽长比?我想问的是我把驱动电路加在mos管的栅极,怎么影响锁存器的变化,按理说时钟mos管只是起采样作用,给时钟信号加驱动电路能有怎么样的影响?

我加了驱动电路,仿真看没什么变化,延迟时间也没有,不明白

电路图

你所说的只针对于仿真阶段,实际中没有那么好的时钟信号。

不加驱动电路,很难驱动DAC