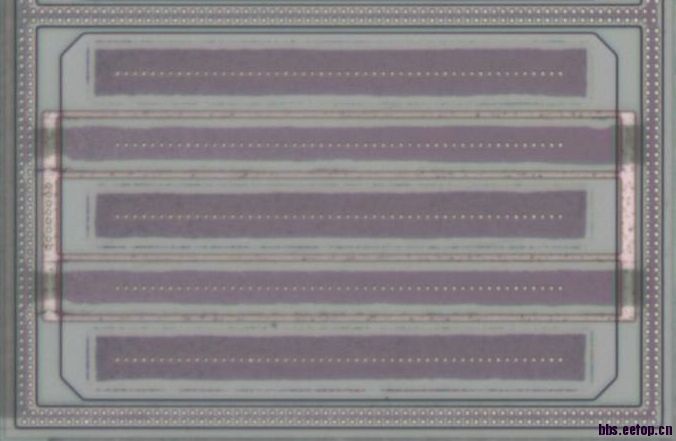

请问这种ESD的版图是怎么实现的?

时间:10-02

整理:3721RD

点击:

请问这种ESD的版图是怎么实现的?

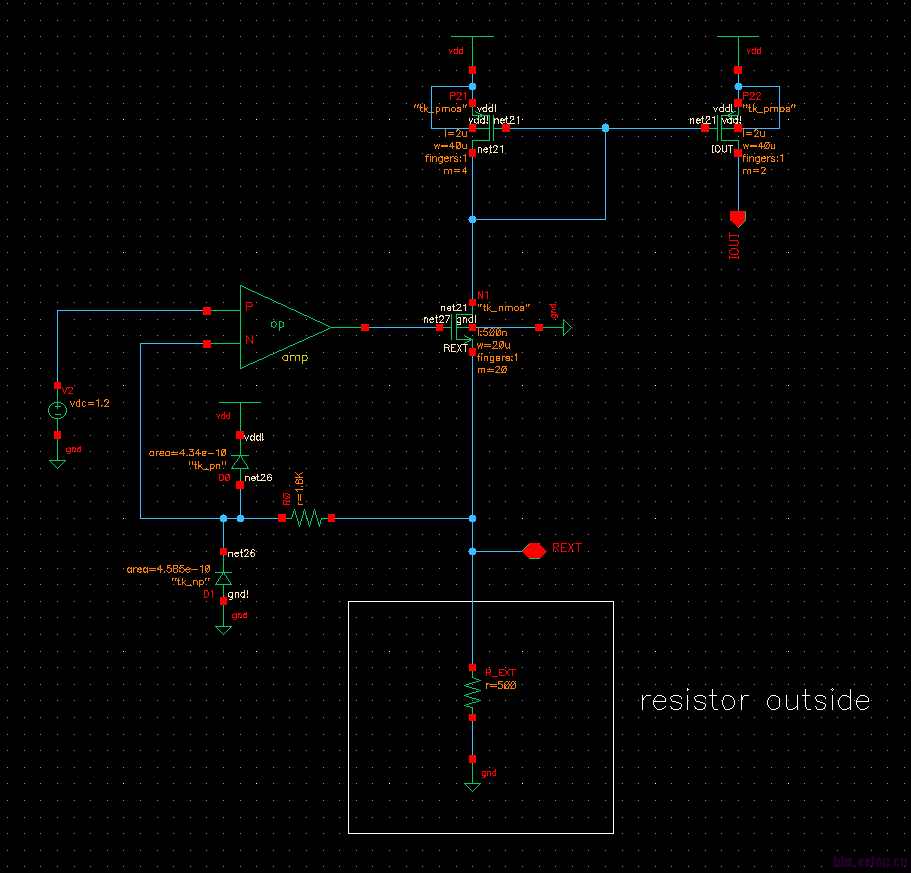

还有,如下面电路所示,芯片需要外接电阻来产生偏置电流,因为压差的关系,N1前面不接电阻,

N1要做成这种ESD layout。但是N1又是运放的一部分,在仿真中还是用普通管子的model吗?谢谢!

MOS管即可,按照foundry的ESD guide做呗。

若没有其他的spice model,可以用mos管的spice model来仿真,但注意将实际的源漏区的尺寸填上。会有一些误差,但也要看foundry给你的管子的spice model对于大尺寸是否准确了。

N1源端和REXT端可以串接一个100欧姆的小电阻,这样N1的源端可以缩小面积,SAB层可以不覆盖POLY

谢谢 , 一般的话用普通MOS管+ SAB层就可实现了吧?