PLL出现了周期滑步现象,附图,欢迎一起讨论。

时间:10-02

整理:3721RD

点击:

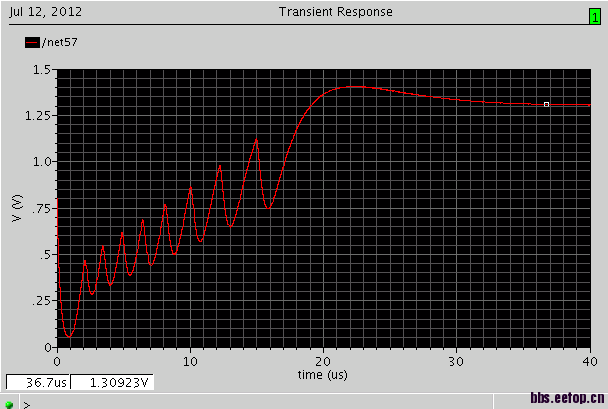

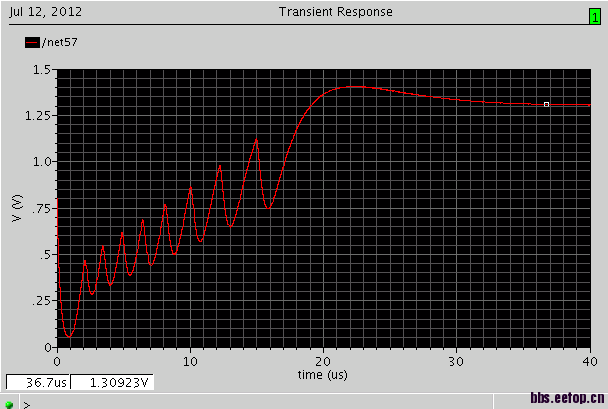

我仿了个PLL,出现了周期滑步现象,大家是如何解决的,是不是BW取太小的原因?

那说明锁定后频率切换一般不会出现滑步,是不是啊?

is this a problem?

如果你是说前面的牵引过程,那是没问题,减小带宽会削弱所谓周期滑步现象。

转换频率时在锁定过程中出现的滑步是正常的,滑步的主要原因是PFD的Ip/相位曲线不是一条直线,而是锯齿线,另一个次要的因素是相位比较不是时刻进行的,是以鉴相频率fref取样的。

带宽和滑步没有任何关系,窄带只是滤掉了滑步的高端频谱,使波形圆滑了,好看一点而已

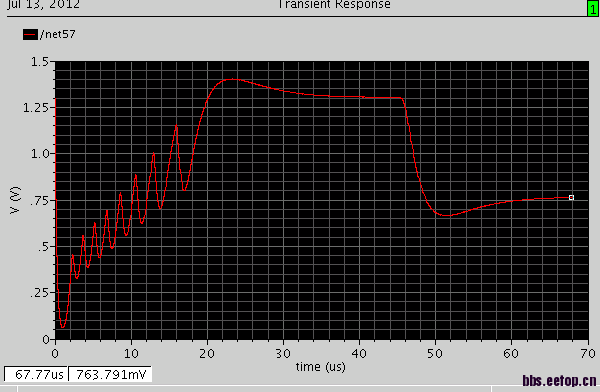

上面那张图是PLL从未锁定到锁定的过程,这个是指牵引过程吗,那个时间是不是叫pll的setting time?下图是张锁定后频率的切换过程,没有出现滑步的现象。

那说明锁定后频率切换一般不会出现滑步,是不是啊?

国半那本书上将环路带宽在(1/100,1/10)的参考频率,如果小于百分之一的参考频率,会出现周期滑步。还有大的频率切换会出现周期滑步,这是啥原因?谢谢解答。