带隙基准为何会受到外部电路的影响?

时间:10-02

整理:3721RD

点击:

带隙基准为何会受到外部电路的影响?

带隙基准为何会受到外部电路的影响?这个问题是什么上面的问题?

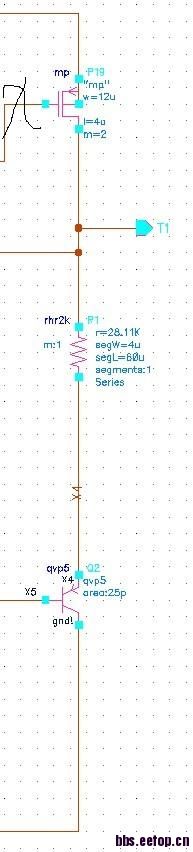

如果所示T1为输出的基准电压

那么如果有或者没有外部电路连接在T1上,为何对T1有影响?

图上x点电压固定

如果外部负载的阻抗不是足够大的情况, 外部负载形成对PMOS管P19的分流,导致流过R1和Q2的电流在不同负载情况下有所不同. 所以输出的带隙基准电压也会不同. 这种情况在超低功耗的带隙基准电压设计中会遇到,如果设计的时候流过的电流本身只有纳安级别, 那么后面接的负载就很容易对内部电路分流了, 导致直流工作点偏离. 所以对这种超低功耗的带隙基准电路进行测试的时候,这也是个典型的问题.

那这一般该怎样处理啊!输出电流总在变。

Using a unit-gain buffer

用单位增益缓冲的作用是?

我t1外接的都是其他管子的栅极,按理电阻很大,可以忽略不计了。为何外面的电话还对t1有影响呢?

别人说了T1连栅极,就没有分流了

没见你的全部电路,不好下结论,一般这种情况不太会出现,仔细检查你的电路连接和仿真的设置。你的基准应该有误。

LZ,很想帮你看看,不过你的表述我看了几遍也没看懂,建议你给个详细点的图,把问题再叙述清楚些。

看看先。

呵呵,他说接到栅极的时候是在我回复之后啦. 我们自己做的超低功耗带隙基准就是有这个问题要注意的,所以我往这个思路上提醒了一下,仅作参考.

的确是有个地方,带隙没有连到栅极,而是连到d端,所以带隙会随外部电路的变化而变化。

那我的提醒还是有必要的啦?

事情的结果是

外部电路改变后,已经完成电路的工作,所以带隙基准不正确也无碍

但问题是

基准怎么可以变化?怎么样才能不与外部电路有关?

后面加一个buffer不就行了?带隙基准的输出连到buffer的输入栅极,阻抗无穷大,不会分流的。