Help! How to simulate transmission gate's on-resistance in Hspice?

时间:10-02

整理:3721RD

点击:

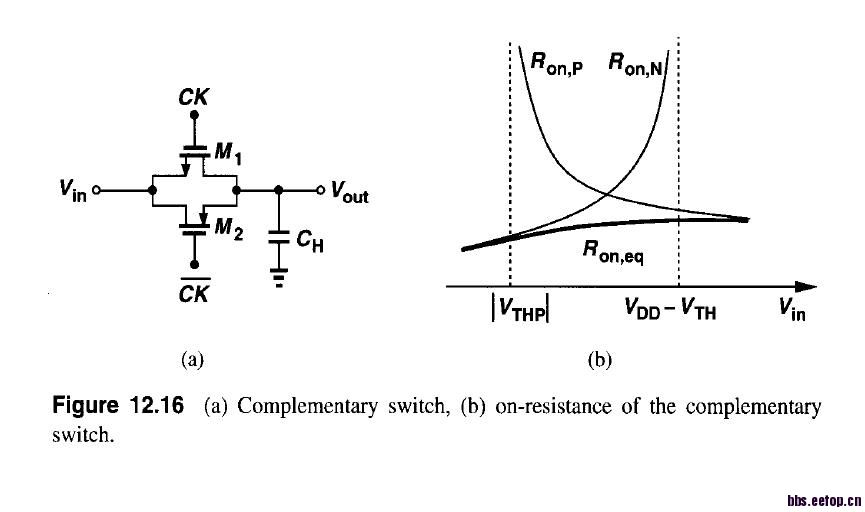

Help me, please.How to simulate transmission gate's on-resistance, Ron,eq, in Hspice?

Please see Razavi Figure 12.16 (b), page 417.

VCC VCC gnd 3.3V

MN VIN VCC VOUT GND NCH3 L=0.35U W=5U

MP VOUT GND VIN VCC PCH3 L=0.35U W=15U

非常感谢你

Help me, please.

手动计算RC 延时,这样可以估算大致的数值,前端设计时足够了,精确的还是要Hspice,

仿真导通电阻,可以用dc analysis和transient analysis。简单的办法如小编图示,用dc sweep分别看p transistor和n transistor的导通电阻,它们的并联就是传输们的导通电阻。

transistor的导通电阻的表示,可以查查hspice manual,我依稀记得是lv*或者lx*。

.probe dc ron1=par('1/lx8(MI2)')

加上這一行即可

DC sweep,然后对曲线求deriv应该就能得到了

Help me, please.

please check your short message

transmission simulate gate Hspice resistance 相关文章: