差分放大器的输入管问题

PMOS和NMOS的选择,一个考虑是输入电压范围,若输入电压较低,应选择PMOS,否则是NMOS,其他的考虑请大家补充!

考虑到匹配和噪声,PMOS更好

PMOS 速度比NMOS 慢吧

有资料上说PMOS的匹配性比NMOS好,不过这一点我自己没有体会到过。

拉扎维书的第二章提到过,NMOS迁移率高于PMOS,因此通常来说速度较快,而PMOS要获得大致相同的速度则要消耗更大的面积。更大的面积,一方面对于工艺绝对误差引起的相对失配就减小了,另一方面,则是芯片面积增加,以及寄生电容增加,影响到了电路的速度;

拉扎维书的第7章又提到,理论上说,PMOS的1/f噪声要比NMOS来的小,而且在实际的设计中,貌似我们也是这么做的。

暂时想到这么多,都是自己的理解,说错了的,楼下的大侠们随便拍

看Ken martin书上有比较过。

感觉是考虑运放1/f噪声的时候选PMOS比较好

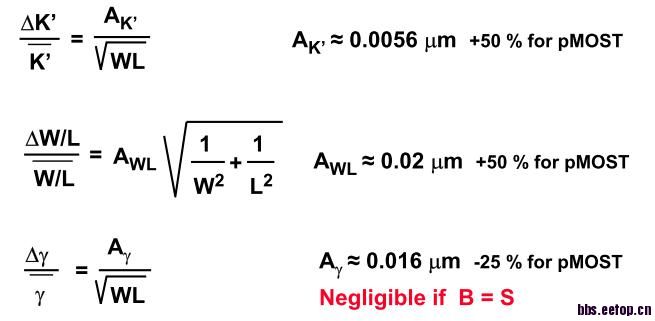

同样面积下pmos的匹配也比nmos好,建议你好好看看Sansen的书

Sansen的书还真没看过,呵呵

在学校的时候没看,工作了吧时间也就少了,加上现在做的方向对这方面没太多需要琢磨的

有时间的确还是该把Sansen的书找来看看了

用PMOS好像较为稳定,也较为经济。

学习了 。

根据 wocaishidac前辈的提示翻了一下书

vth的情况也是P的大50%,

sansen解释道用P是因为b接s,衬偏调制效应那个因子忽略,当然看系数p比n好也不会很明显

如果b不接s,那么同尺寸的p的失配比n的大,

我在网上看的:

采用PMOS管作为差分输入级,这样可以降低输入共模电平,还具有比NMOS管更好的1/f噪声特性,提高电源抑制比。

对于折叠共源共栅跨到运算放大器而言,NMOS输入对管具有较高的跨导,能使运放达到较高的直流增益,但需要采用PMOS作为共源共栅管。在同样的偏置条件下,PMOS管的跨导为NMOS管得40%~50%,从而限制了运算放大器的次极点频率。如果采用PMOS作为输入级,运放则具有较低的噪声和较高的次极点频率,噪声较低,但直流增益较小。

说实话,不是很理解,呵呵

这一部分内容,拉扎维书的第9章讲得挺清楚的吧(中文版的248~250页)那部分。

说的都是Folded cascode OP AMP的特性。

谢谢!

看来好好看书还是有必要的

bucuo...

看书很重要啊

你确定嘛?为什么foundry提供的offset都是P管小?

你的pdk说明offset的地方方便截个图么?

不确定,只是在桑森的书上看到的,

而且是在相同尺寸的前提下,pmos默认就是源衬相连的,按桑森的说法,p的应该稍微好一点,但是看公式,优势不会很明显,

实际中相同的跨导,p的尺寸肯定更大,匹配更好吧

希望大牛给出清晰正确的答案!

deep sub-nano,PMOS offset is much higher than nmos

主要就是看input swing, offset,noise,psrr影响并不大,就是p管的gm小,同电流下size大,匹配好,flicker noise小

nmos一般用于高速器件吧