关于电荷注入的问题?

一个很简单的电路,由一个nmos开关和一个电容构成,由图1所示.输入信号是一个三角波,100KHz;时钟频率2MHz.

问题: 当开关关断时,输出电压理想上会保持,但实际会有一个误差电压,误关电压大小由开关管的尺寸决定,尺寸越大,误差也就越大.我就想知道这个电压到底是由电荷注入引起的,还是由时钟溃通引起的?如果是由电荷注入引起的,根据拉扎维书里的误差电压公式计算,误差值很小,是纳伏级的,可实际是毫伏级的,所以不知道仿真能不能仿出电荷注入效应.

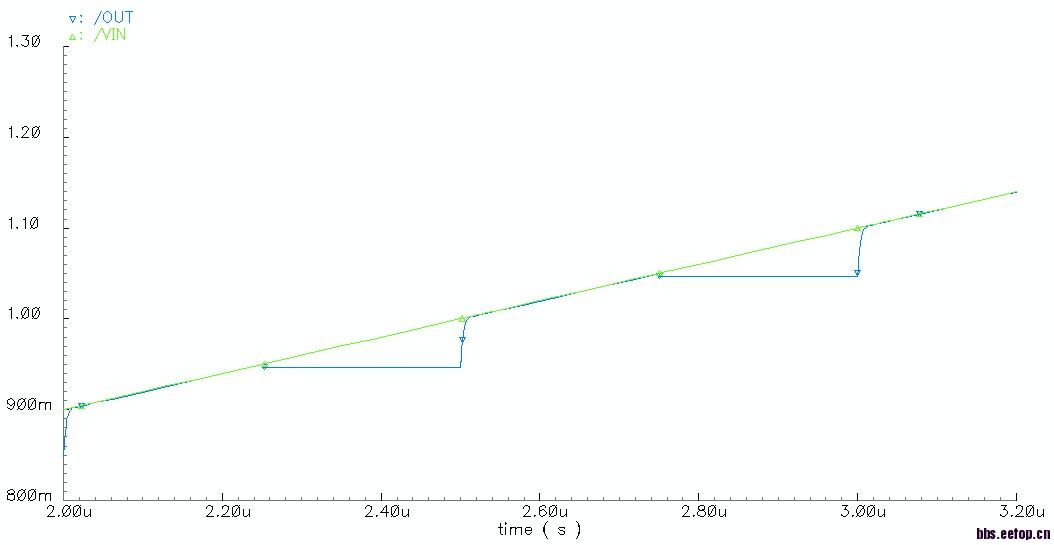

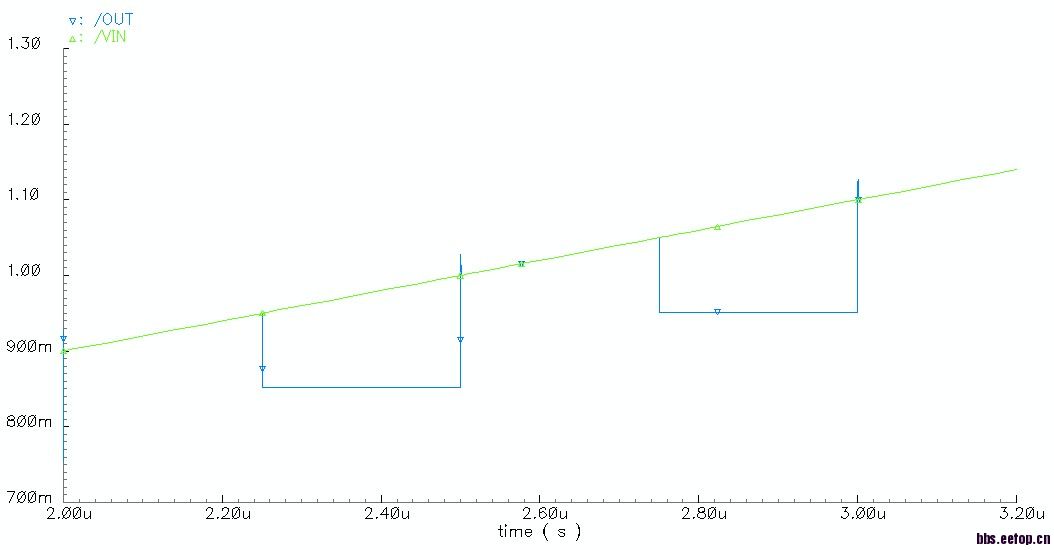

注: 图2是开关管尺寸较小时的瞬时波形;图3是开关管尺寸较大时的瞬时波形,它的误关电压已达到100mV.

图1

图2

图2 图3

图3

应该是两者共同引起的吧

这个误差真的很大,与管子的尺寸有关系,而且仅是在开关关断时会出现,而开关导通时没有误差.如果是时钟溃通,那在开关导通时也应该有误差电压出现才对,可实际仿真也有一些影响,但不明显,主要是关断时的误差特大,那么能说明这是注入引起的吗?

这个应该是由寄生的电容引起的馈通。关断时信号下拉引起的。

尺寸越大效应越明显。

有点奇怪,先看时钟馈通,相当于两个串联的电容,下面是采样电容C0,上面是CLK到OUT的等效电容,设为C1,C1的值决定于工艺和尺寸,看图中电路,不过几个 fF,引起的电压变化为 V(CLK)*C1/(C1+C0),貌似不会引起这么大的电压下降。

再说沟道注入,假设沟道电荷的一半注入到采样电容C0,这一半的电荷为V(CLK)*C(channel),这里的C(channel)约等于上面的C1,最后引起的电压变化约为 V(CLK)*C1/C0,与上面的数值接近。

两部分加起来,会引起这么大的电压降吗?

那就是说实际当中,时钟溃通的影响要比电荷注入大得多?那拉扎维书上关于抵消电荷注入的方法在实际当中并不会起到多大作用?比如加dummy开关.那我就主要关注如何消除时钟溃通的影响就行了吧?

1. 开关在关断前是在线性区的,它的栅漏电容是不是应该等于栅氧化层电容的一半,再加上栅漏交叠电容?当开关管尺寸较大时,比如w/l=100u/0.54u,从仿真看,它的栅源或栅漏电容都有四五十飞法.

2. 你说的C1是不是指的是栅漏或栅源的交叠电容?而C(channel)应该是栅氧化层电容吧?应该不一样吧?如果按照时钟溃通的来计算,确实有一两百毫伏的误差电压.看来时钟溃通比电荷注入影响大多了.

我只知道尺寸越大,效应越明显。

要减小可用传输门试试。

肯定是时钟溃通引起的,在这种电路设计里,我一般都采用最小管子;还想再小的话,控制Vgs试试,但这个跟输入电压有关,不好控制,但可以设一个最高值来控制