apamp 运放问题

时间:10-02

整理:3721RD

点击:

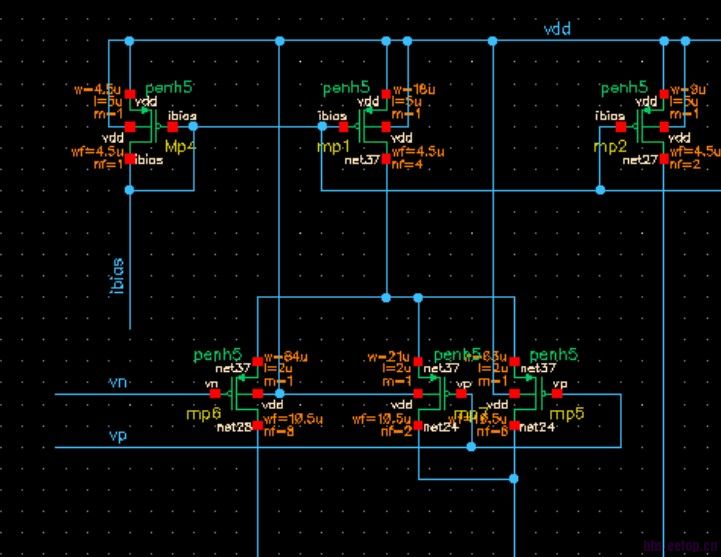

运放的输入对如上图,这种结构是引入迟滞,还是消除失调?具体的工作原理是什么?

我在IEEE中差了很多文献都没找到相关的。希望帮忙解答。

另外有个问题用什么工具mos画图比较好,当在word中编辑电路原理图时?

引入迟滞更合理一些吧?不可能消除失调的。可以跑一下tran比较一下两个的结果。

画图,都用visio吧。

我也偏向于这个结论,但其工作原理是怎样的啊?

不是迟滞哦 迟滞必须引入正反馈才行哦

这个是为了保证延迟要求做的不等比输入管。

4# 说的有道理

都是扯淡的东西,

仔细看看图,不是一样的东西么

一个是10.5/2*8另一个是10.5/2*6 + 10.5/2*2

搞笑啊,原来把8拆成6+2就会有迟滞和失调了

虽然数学公式是一样,但是layout的时候大小还是会不一样的~ 左边那个寄生电容会少一点

想问一下,这个comparator应用在哪里?如果真如#7所说,是由于寄生电容的差异造成propagation delay有差异(我认为这个差异在于上升和下降delay time),这一特性对你有什么用呢?

难道靠寄生调整啊

我们做东西都是要求可控的

逗你玩。

这个不太懂啊

小编没说用在哪啊~

电路很诡异,可控性太差!

高手啊

不明白了,这靠layout调整?