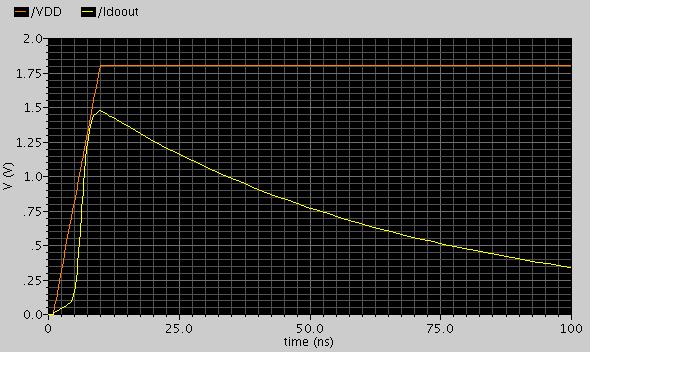

LDO稳不住 ,上去又掉下来了 怎么办?附cadence图

内部误差放大器单独仿真过,没有问题的啊。

然后再加了参考电压,PASS元件,取样电路等

不知道怎么回事?

请教大侠们支招解释

负载加的多少?1.8V你的电路能正常工作不?

还有仿真时间也太短了

lz 把电路也贴上来啊

给人感觉好像驱动能力不够似的,看看你的负载,还有就是check下你的电路在1.8V下能否工作,bandgap正常工作起来也要2V吧,^_^。

感觉你的仿真存在问题,LDO的输出通常会加1uF左右的电容,单纯这个电容充电的时间已经远远超出你的仿真时间了。建议将Transient 的结束时间设定的更长一些,500mS左右。还有,还应该给大家提供详细的参数:

工艺

输出负载

输入输出电容

==

单纯从你的结果来看,很难断定原因。

i同意楼上的。仿真时间也太短了。

模擬的時間太短了, 如果輸出有掛電容的話應該要到us級.

谢谢大家

我的是0.18微米的1.8供电仿真时间我仿真到50US的,这里只是突出电压掉下来的过程,所以将时间缩短了。

这里是给VCO供电,所以负载电流不超过10毫安。负载电容小于1PF。

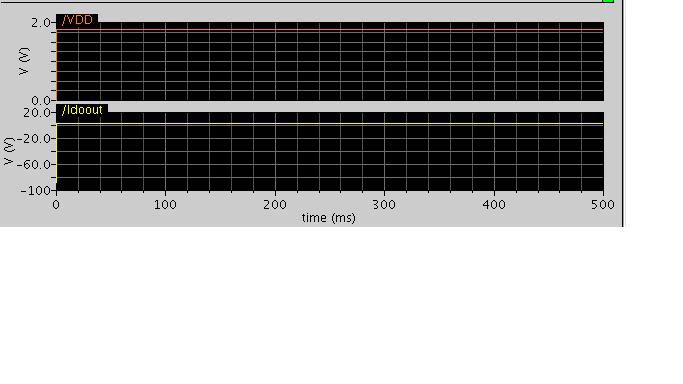

电路仿真500毫秒后,还是停留在0伏。

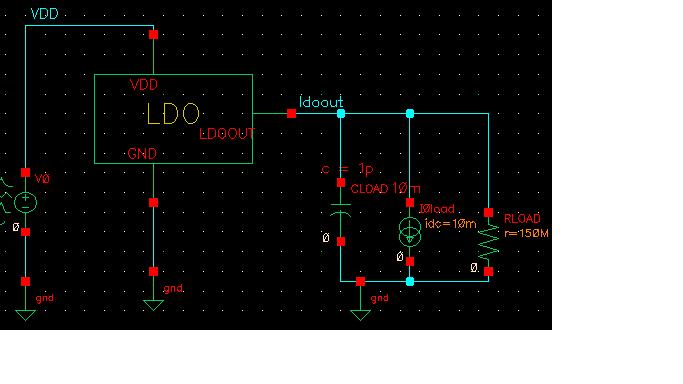

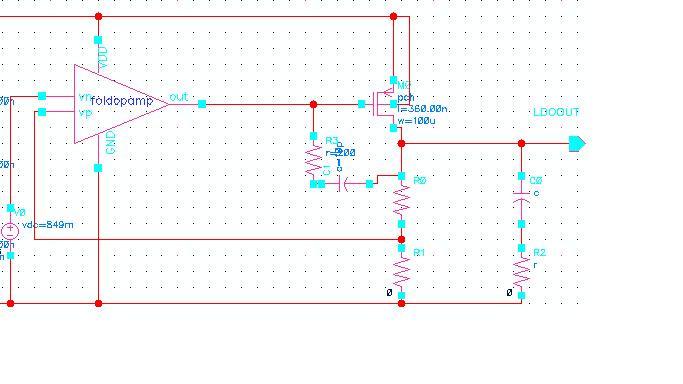

后面是电路图。请教各位大侠,帮忙分析分析

这里暂且用理想电压源替代bandgap

会不会vin和vip接反了?

你用了一个10ma的电流源作负载,明显你的Pmos提供不了这么大的电流拉,

所以说是你的输出级驱动不够阿,

所以,把10ma电流源换成1ma或者更小的试试,或者把你的Pmos做大100倍,10mA的电流很大了,Pmos小了是肯定不行的。

你改变Pmos的时候注意稳定性和电容补偿方面的问题同意楼上的

output pmossize TOO SMALL !你的启动电路呢? work了没有?

1. 有些 ldo使用 nmos 因為 nmos RDS 比 pmos 小而且 OPA 是 負回授做 compensation 比較easy但是 nmossub 得接 gnd會有 body effect2. 如果改使用 pmoscompensation 要處理好還有加大 pmos size對拉要sim dymaic loading很多 ldodc loading 會ok但是 如果10mA@1us[/email]switch下 , 會知道 問題但是 如果 你這 ldo 後面給 ic 內 電路一但 當內部 low volt switch特別是 只有 1.8v那應該 是logic block ..switch 時 問題相當多多串幾級 compensation 可以解決但是 會複雜

要不我给你一个得了 晕死 我一天做3个都没有出现你的问题再说了 就这么几个管子 不可能找不到原因你先不要仿VDD开启直接给vdd1.8变换负载 看卡你的电路是不是work完了再给vdd一个阶跃这样的话确定 你start有没有问题再就是 你的pmos差不多 应该可以着的看你地下的分压电阻给的大小是不是power线性了?你的load这么小 用什么ldo啊用个buffer就ok了

同意!接反的可能性相当大,应该看看PMOS的gate电压。

同意楼上的 !

这个是什么软件?

哈哈 你真的舍得给我一个能够work的电路的话,那就太好了。我就可以比对我的设计了。

我按照你的方法,先没有仿真VDD开启。 直接给VDD 1.8伏,变换负载电流从1mA~ 10A,LDO的输出都稳定1.768伏, 压差只有32毫伏。

但是仿真VDD开启(给VDD阶跃)的时候,LDO就没有输出了,输出0伏。

这个问题会出在哪里?

其实我的电路里面PMOS也不小了。上面显示的是单个的,没有显示并联个数M。

回复 eemike这是cadence

谢谢指点。

按照另外一个网友的意见。我先仿真VDD=1.8(不仿真开启),变化负载电流,LDO输出基本稳定在1.768V , 压差32毫伏。

不过,若VDD换成阶跃信号(模拟加载电源过程),LDO输出则一直在0伏。

【但负载电流变成60 UA或以下的时候,则LDO输出1.8伏,等于电源电压了。若大于60UA以后,LDO输出基本是0伏特】

我改了PMOS的尺寸,还是不能解决问题。

弱弱的问问改变PMOS尺寸的时候,如何考虑稳定性和补偿?谢谢 受用了。

有时间的话给我们详细介绍介绍,上上课,呵呵。

我的电路会是什么问题呢?

另外 一个网友问 有启动电路没有?我没有设计bandgap(包括bandgap启动电路),直接用直流电压源做误差放大器的参考了。

还需要其他的启动电路吗?启动什么地方?可以不要启动电路

你的负载能力比较小了,注意线路接发,跟踪一些可疑的节点

如PFET的gate, FB你的系统存在两个低频极点(M0栅极和漏极),补偿不好的话是不稳定的,做AC分析没问题吗?

负载用的是什么?

负载用电容 理想电流源和大电阻模拟VCO负载。

谢谢上面的几位朋友。我再试试。我仿真了PSRR

对于来自LDO电源输入端的高频电源噪声,有较好的滤除能力;

但是对于低频电源噪声,LDO输出端几乎没有衰减 的呈现出来。

不知怎么改进?

运放的开环增益?

用的什么工艺?

用理想电压源替代bandgapm