关于小数频综的问题

时间:10-02

整理:3721RD

点击:

本人在研究小数频综,由于是新手,很多不懂,想请教一下

我先在simulink里建立一个pll模型,系统参数还是采用以前做过的pll的参数,

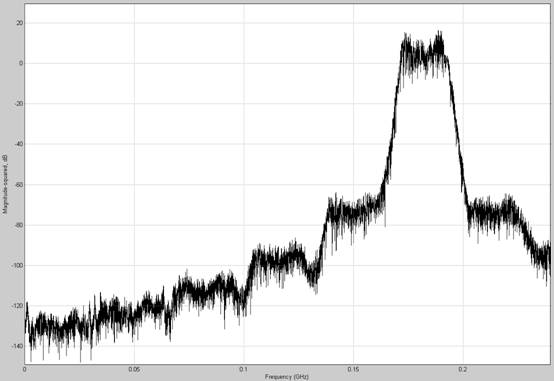

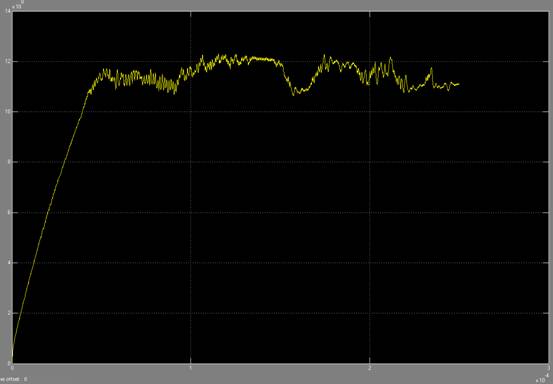

再自己又写了一段三阶sdm的verilog程序,将仿出的数据导到simulink里面,控制除频器的除数,最后仿出的vco输出频率曲线和频谱贴在附件中。

输入频率为33.3M,除频器在5和6间切换

从中可看出,vco的控制线抖动很厉害,输出频率变化10M多!

由于还是不太明白sigma-delta的原理,我觉得既然除频器不断在切换,vco输出抖动应该是必然的呀,怎么做到输出不变呢?

再问两个问题:

1.我的sdm代码可能有点问题,网上有现成的可以参考么?

2。设计小数频综时,系统参数的考虑和普通频综有什么不同呢?

多谢

我先在simulink里建立一个pll模型,系统参数还是采用以前做过的pll的参数,

再自己又写了一段三阶sdm的verilog程序,将仿出的数据导到simulink里面,控制除频器的除数,最后仿出的vco输出频率曲线和频谱贴在附件中。

输入频率为33.3M,除频器在5和6间切换

从中可看出,vco的控制线抖动很厉害,输出频率变化10M多!

由于还是不太明白sigma-delta的原理,我觉得既然除频器不断在切换,vco输出抖动应该是必然的呀,怎么做到输出不变呢?

再问两个问题:

1.我的sdm代码可能有点问题,网上有现成的可以参考么?

2。设计小数频综时,系统参数的考虑和普通频综有什么不同呢?

多谢

频谱

输出频率

我觉得你的delta—sigma modulator有问题,建议你先计算dsm的输出PSD,观察其波形是否正确。