请教关于Z-stack内存问题

时间:10-02

整理:3721RD

点击:

在ZigBee中,分配有8K的SRAM,现在我开房项目遇到内存不够用情况,然后也网上查找了解决方法,有几个问题想请教。

解决方法有几个:

1.优化代码,这不用说的了。

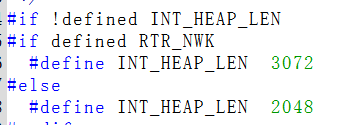

2.减少栈内存:(如图,修改XDATA的值)

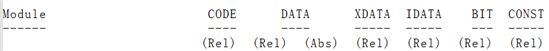

3.堆内存:(如图,修改3072,将它修改小)

4.我在map文件中的发现,这几个占用的XDATA比较大,当然还有其他,其中就修改uart对整个协议栈的影响应该会小一点的,可是我查看了h和c文件并没有想象中那么大的。

问题:

1. 解决方法2和3中,对于 TI纯协议栈 减少到多少比较稳妥的。

2.解决方法3,这些文件中有没有可以减少内存的呢?

3.还有其他的减少Z-stack内存的方法么。

谢谢各位了。

同样关注 期待回复

若是实在不够的话,可以采取外部MCU+CC2530的方式

比较想了解缩减空间协议栈能接受到多少 缩减后会对协议栈造成什么影响

我也一样,另外加入MCU,想要读写取相应的数据速度又更慢了。

我想调整下协议栈的大小 又不敢动 现在内存已经不够了