CC2530F256 的内存分配

各位大师:

大家好!第一次发帖,请多多包涵。

本人最近在做一个项目:利用CC2530F256芯片进行开发,其中要求功能之一为对射频芯片的IEEE地址进行软件修改,即对flash的write操作;看了许多帖子总结出如下几点:

1.IEEE地址在flash里的0x3FFE8--0x3FFEF处,对该区域内容进行修改;

2.不能在运行程序时写flash,应该将write代码复制到sram中:HalFlashRead(PAGE_OF_RAM_CODE, OSET_OF_RAM_CODE, ramCode, SIZE_OF_RAM_CODE);

其中,#define PAGE_OF_RAM_CODE 51 #define OSET_OF_RAM_CODE 0x6DD #define SIZE_OF_RAM_CODE 0x23

这是参考Z-STACK里的配置来的(问题的源头!),但我又不知道代码是从哪个地址复制过来的,

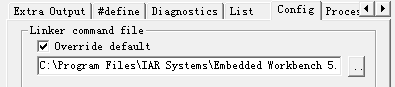

链接文件使用的是默认的F256.xcl,

尝试了使用Z-STACK里的f8w2530.xcl,结果程序完全瘫痪;

3.调用HalFlashWrite(),该函数调用了触发write flash的核心代码(复制到sram里的代码)

HalFlashErase(0x7F); writeWord(0x7F, 0x7E8, nID ); ----写之前先擦除

结果,报错

所以,发个帖子请教各位高手,问题如下:

1)CC2530F256的内存配置是不是可以通用Z-Stack里面的CC2530内存配置,具体的RAM_CODE_FLASH和RAM_CODE_XDATA起止地址应该为多少,如何对.xcl文件进行相应修改?

2)对IEEE地址软件改动的流程是不是合理正确的?

拜托各位了,这个项目时间很紧,本人纯属开发届菜鸟,还请各位多多指教,给些建议和想法,多谢多谢!

这个问题已经解决了,解答如下:

1.CC2530的flash是在CPU方式写的时候要将代码复制到SRAM中,这个过程也是十分的繁琐,所以一般不建议采用CPU写方式;

2.采用DMA方式,可以在运行时改写flash(网上有些帖子有误),按照CC2530的用户手册上的步骤写flash——

(1)先设置将要使用的信道(0-4)地址DMAxCFGH:DMAxCFGL,这也是我上述问题的关键点,一定是先配置好信道地址。详见datasheet里8.3节;

(2)然后指定所使用的信道,对DMA Configuration Data Structure进行配置,并且“arm and active”;

(3)写操作

3.具体的代码,可以参照Z-STACK里的writeflash(),但是它之前已经对DMA的初始化了,自己写的话还是需要要增加步骤(1)的;

希望对有需要的人以帮助,谢谢捧场!

牛,收藏,以后应该会用到