TPS53219A 电源问题-输出端接电解电容和陶瓷电容,load电流差距好大

输出端是电解电容的时候load电流最大是25A

输出端是陶瓷电容的时候load电流最大是8A? 怎么会区别这么大。

输出端是电解电容的时候load电流最大是25A

输出端是电解电容的时候load电流最大是25A

输出端是电解电容的时候load电流最大是25A

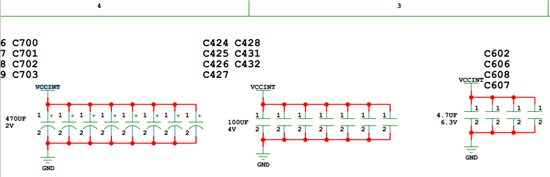

如果我在 fpga电源引脚端并联0.1uf电容,22uf陶瓷电容,或者其它电容 会不会改变电源的ESR,

亲;有差别是正常的。不过,感兴趣的是,你用啥工具测的电流?

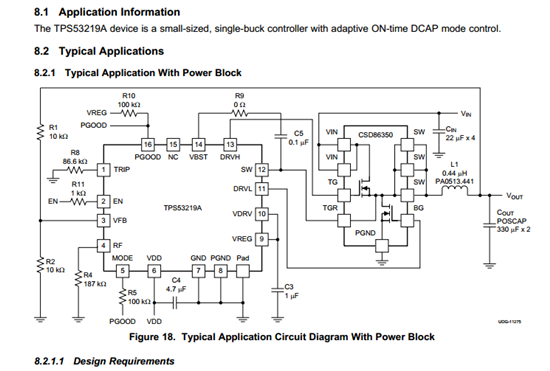

Hi,

电源本身没有ESR,ESR是输出电容上的。用不同容值组合并联来做输出电容,是因为不同容值大小电容的频率阻抗特性不同,并联0.1uF和22uF(引脚附近一般好像不会用这么大,4.7uF就足够了)是为了获得很宽频率范围内输出电容网络很小的阻抗。简单理解,0.1uF对高频响应较快,当负载突变时,由0.1uF的电容率先提供电荷,然后是较大一点的电容。这就是为什么FPGA的去耦电容要求越小的越贴近FPGA电源引脚。

谢谢!

Hi

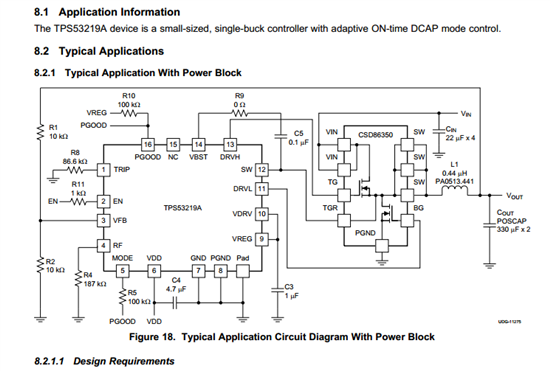

这只是2个案例,输出电流设置到8A,并不意味着陶瓷电容时最大输出电流时8A。 TI的EVM板用的就是陶瓷电容,输出电流设计到25A: http://www.ti.com.cn/cn/lit/ug/slvu431/slvu431.pdf

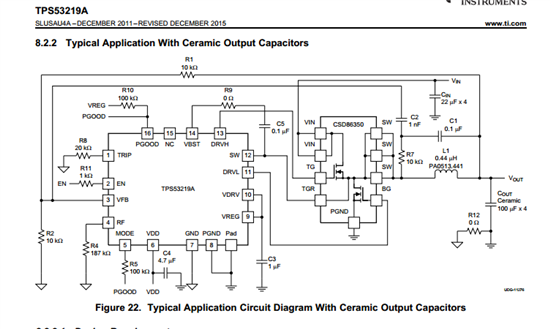

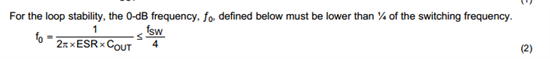

输出电容选择陶瓷电容还是SP-CAP, 你还是需要理解DCAP的控制模式,在这个模式下不能选择太低ESR的陶瓷电容(难以稳定),而选择SP-CAP。 如果选择陶瓷电容,你需要在反馈额外增加ripple信号。具体看datasheet第二十一页。

谢谢回复

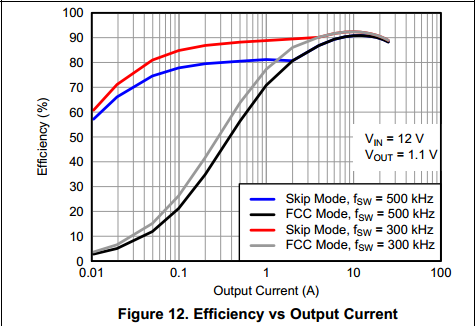

Skip Mode, fSW = 500 kHz的时候,我看线只画到了2A左右,这种skip mode只能输出到2A?还是后面的线没画,或者是与FFC mode的线重合了?其实是到25A?

这些电容是要接在FPGA 那边的,但是这些电容会影响电源的 ESR吗? 这些距离电源输出端是有一定距离的

vout 接VCCINT

Hi,

后面的是重合了。重载情况下进入CCM模式,已经退出Skip mode了。

Hi,

我想是不是可以这样理解,导线本身是不理想的,有电阻和寄生电容电感。反馈信号取自靠近电源的输出电容,也就是说环路在尝试稳定住反馈点处的电压,那么可以把靠近FPGA输出电容的ESR、导线上的电阻电容电感都归到负载一侧。从这个角度理解,靠近FPGA去耦电容的ESR对环路没有影响。