TPS62130RGT 不能正常掉电

TI工程师您好:

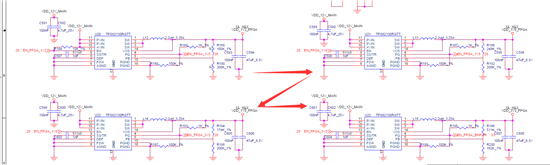

我用 TPS62130RGT 芯片给FPGA电源做上电时序,具体思路是通过前一级电源的POWERGOOD引脚接到下一级电源的EN引脚来实现。

现在遇到的问题是:上电时序是没问题了,但是想给FPGA掉电时候却发现电源不能正常掉电。

表现为EN脚为低电平(100mV,低于低电平范围)时,仍然会有一个很低的电压输出。

当最前一级电源芯片的使能信号 EN_FPGA_1V2 为低电平(约100mV)时,VDD_1V2_FPGA输出并不能真正关断,会有300mV左右电压输出;

这样导致下一级芯片的EN信号会有300mV左右,VDD_1V8_FPGA输出有0.5~0.6V电压。

再下一级芯片EN信号有0.5~0.6V电压,导致VDD_1V5_FPGA会有0.9V左右输出。

这样,最后一级芯片EN信号为0.9V,导致3.3V输出一直是有的,不会随着前面电压掉电。

请问

1、TI工程师们对此有什么建议?

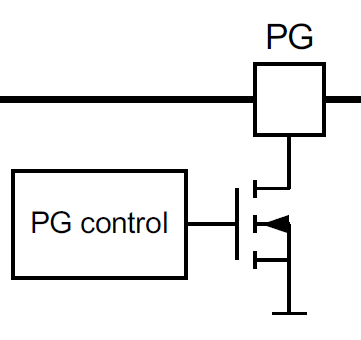

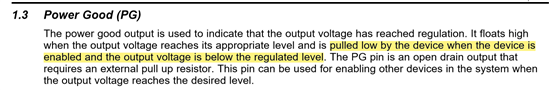

2、当芯片供电正常(PVIN供电正常),而EN为低电平时,PG引脚的状态是如何的?是输出低电平(MOS管导通)?还是输出高阻态(MOS管关断)?

内部MOS是关断的

尝试将PGOOD直接用100K和Vout相接,移除下方100K的接地电阻,看是否有同样的现象

有的话,用示波器抓取一下Vout和PGOOD信号

谢谢您的回复。

设计时候我有考虑过只加上拉,去掉下拉的情况。但是在芯片供电正常,EN为低电平时候,PG脚的状态是应该是悬空状态(PG脚的MOS关断,100K上拉的电源也无输出)。 基于这种情况我加了下拉电阻,确保当EN为低电平时候,PG不会输出悬空状态,而是输出低电平。

稍后我尝试按照您方法把上拉改为100K,下拉去掉。VOUT 和 PG信号我也会用示波器看。

Hi

将100k电阻加大到500k电阻看看效果/

这样PG低电平电压输出时会不会尽量低一些。

FPGA不能正常掉电的原因找到了。

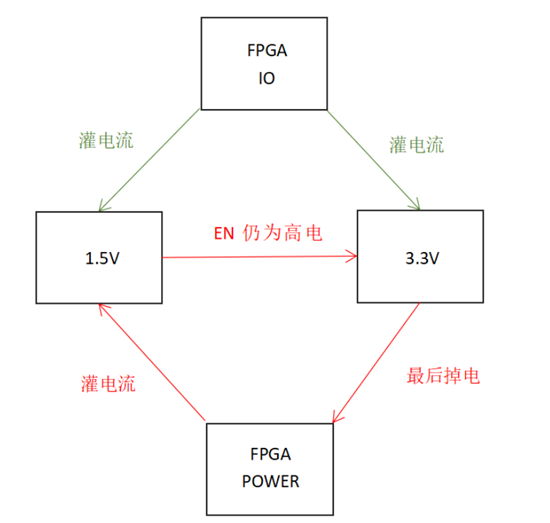

1、FPGA上电时序要求为 1.0->1.2->1.8-> 1.5-> 3.3 ,掉电时序为 3.3->1.5->1.8->1.2->1.0,而目前我这个设计只考虑了上电时序却不能满足掉电时序。目前的设计的掉电时序是1.0->1.2->1.8-> 1.5-> 3.3 ,3.3V最后掉电,导致3.3V会通过FPGA会对其他电源形成灌电流。

2、就算FPGA 的供电全都断掉了,FPGA 各路电源上仍然能测出一定电压(3.3V电源测得有1.4V电压)。原因是FPGA的外设没掉电,外设通过FPGA对各路电源形成灌电流。