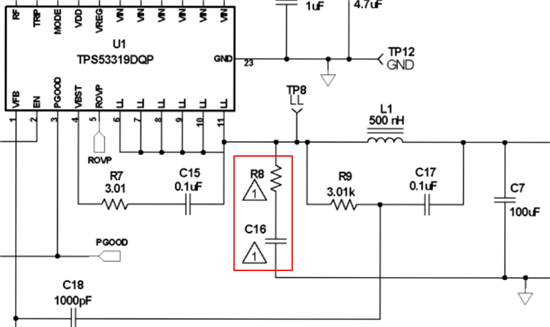

TPS53319 DEMO板原理图上LL与GND之间预留RC作用咨询

TPS53319在我的板上轻载使用时正常,到5A时板子出现异常。TI的TPS53319 DEMO板上LL pin和GND之间预留了一个RC电路,在我的板上焊接RC后,故障现象有所改善。我想请教这个RC电路的作用,以及如何调整。

Hi

降低高边MOS在启动时出现的spike.

Hi

相关计算参考附件。

你是什么故障,加RC只能改善SW的上冲电压峰值,如果你的环路问题,更改RC是没用的

我们这边发现,TPS53319电源模块工作起来,并且在带载5A时,会影响我们板子上其他功能(DDR)的正常运行。然后在SW网络上加1.5nf-3.3nf的对地电容,能改善这个干扰问题。但是发现在电容加大后,SW的上升和下降沿会出现回沟。另外在加大电阻时,振铃数量会变少,但是上升沿会变陡,还是会引起干扰问题。所以目前我们只加了一个2.2nF的电容,没有加电阻。不确定,这样能否彻底解决问题。

另外,请教一下,怎么确定环路是否稳定?

环路的话,你看SW波形和Vout是否稳定。

建议上传一下你说的几种条件下的SW节点和输出纹波的波形。

谢谢大家的回答。

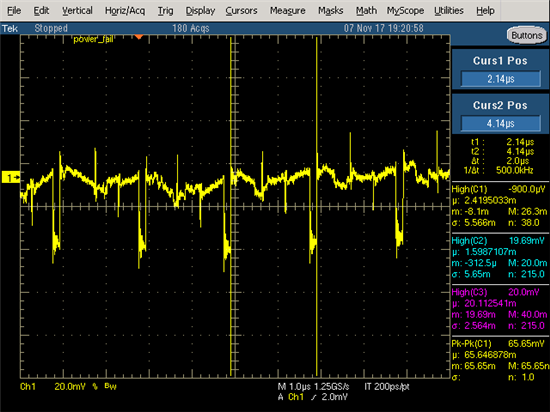

我试了多种RC组合,其中LL与GND之间加3.3nF+0ohm效果最好,实测波形如下:

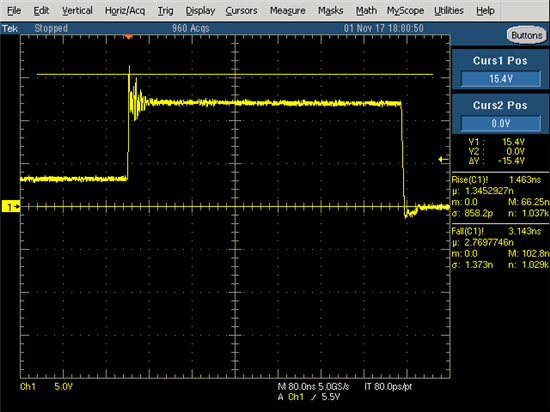

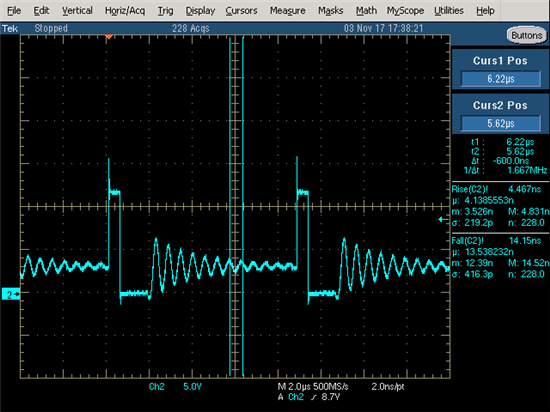

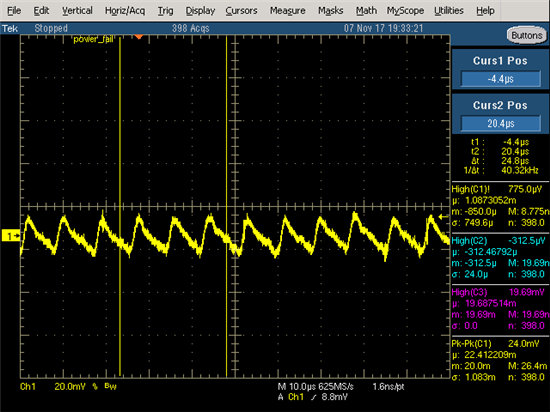

LL与GND之间没有加电容和电阻,LL波形

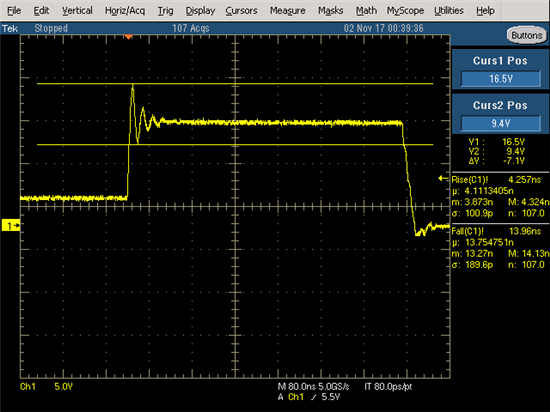

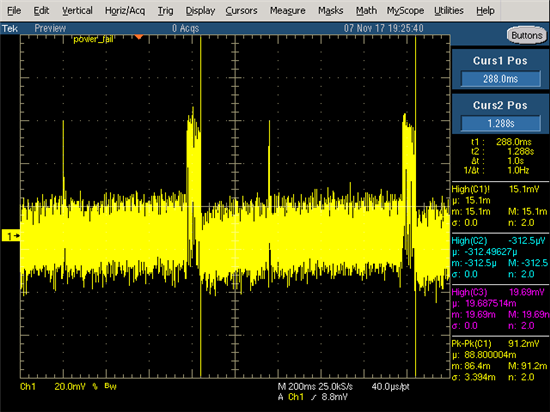

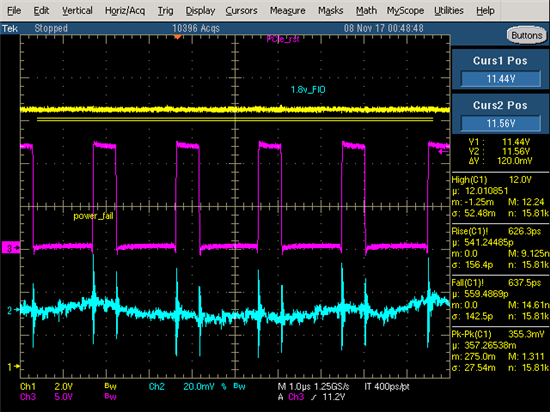

LL与GND之间加3.3nF电容,LL波形

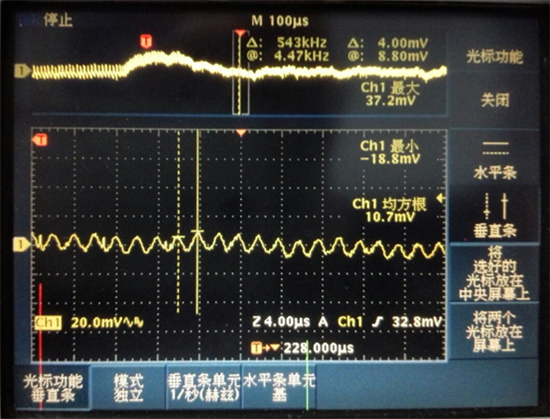

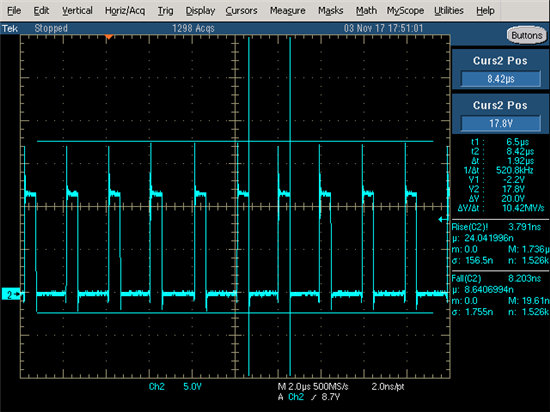

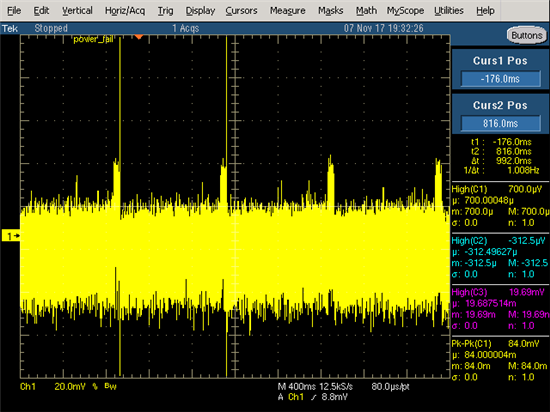

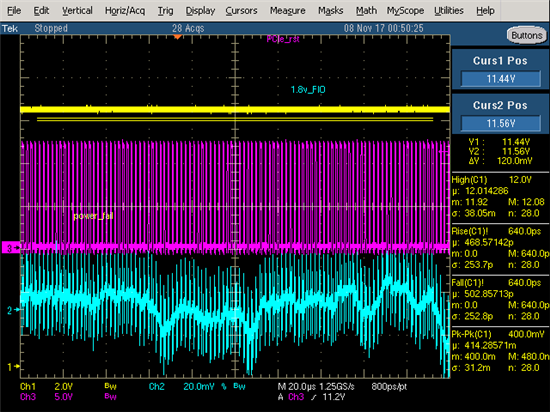

LL与GND之间加3.3nF电容后的纹波展开

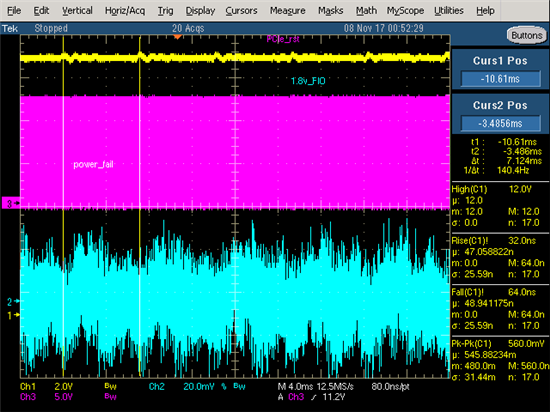

LL与GND之间加3.3nF电容后的纹波

请问改后这样环路是否算稳定了呢?

你的输出纹波不对,建议你对照数据手册的波形

SW的需要多个周期的波形,你SW波形在上管关断时,应该是接近0V,但是你图中却不是,你多几个周期的图放上来

图1: 轻载时SW波形

图2:带载时SW波形

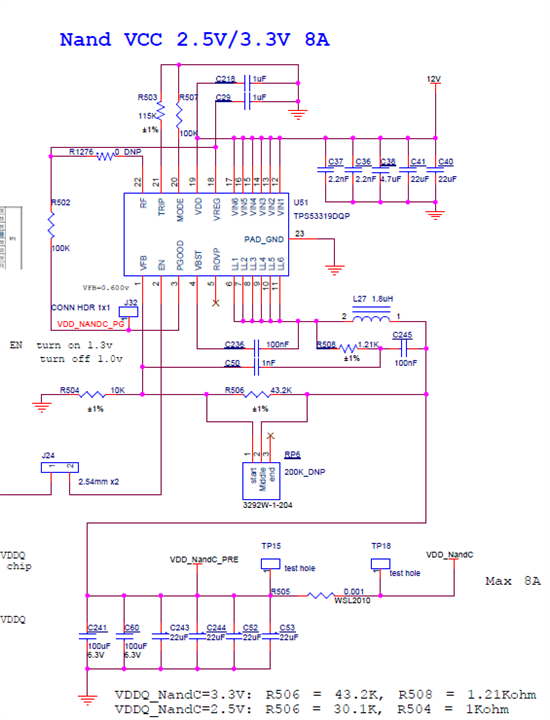

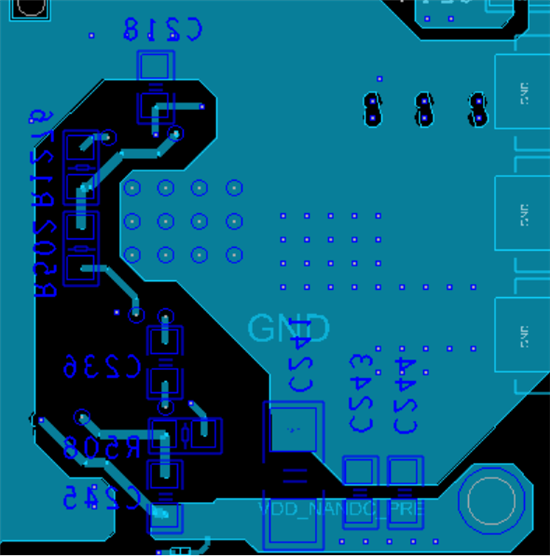

图3 原理图

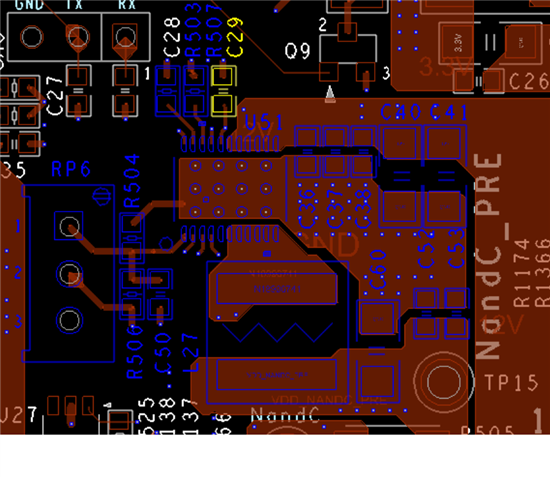

图4 PCB Top

图5 PCB bottom

帮忙看一下 原理图/PCB 有没有什么问题 谢谢, 另外,今天又发生DDR功能异常问题,像是还有哪个电源在干扰DDR.

相关图片看附件,帮忙看看原理图和PCB 有没有什么问题。另外,今天又发现DDR问题了。像是还有电源模块干扰。我们板子上用了5个TPS53319/8模块。

你好,相关资料见附件,帮忙看下原理图与PCB有没有问题。

另外,我们今天再次出现了DDR问题,我们的板子上用到了5个TPS53318/TPS53319模块,好像还有电源干扰了DDR。

看了你的原理图基本没啥问题,你的PCB是几层板呢?如果是两层板,那干扰的确会 比较严重的,一定要用4层板,尤其大电流

你现在波形是正常的,就是SW的ring稍微高了点,加Snubber应该是可以解决的。

关于你的干扰,是怎样的一种干扰呢?你的输出纹波能否上传一下,上次的那个纹波不对。

测试条件:R = 1ohm,C snubber = 3.3nF.without boot resistor.

图1:时间轴为1us时的纹波。

图2:时间轴为200ms 时纹波

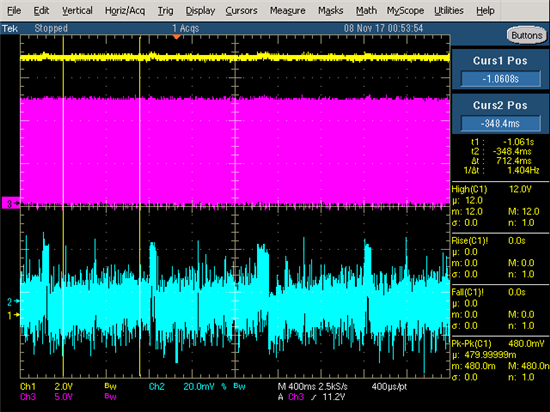

图3 时间轴为400ms时的纹波

图4:空载时的纹波

我们的负载,有周期为1s的大负载特性。

帮忙分析一下,如何解决这个干扰问题。谢谢

将你的Vin(DC),Vout(AC),SW(DC)同时放在一个图内,并用20MHZ,谢谢,

这样看找不出从哪里来的1Hz。

黄色是12V输入,紫色SW,蓝色输出纹波

检查一下输入的AC,貌似这个低频信号是输入端耦合过来的

多谢各位的协助分析!

我们现在将这路53319的12V输入割断,然后用DC supply来单独供这一路电源,目前系统正常运行超过了23小时,还在测试中,但负载端纹波还是有1Hz的规律波形,所以,这1Hz波形应该还是负载特性引起,而不是输入端耦合进来的,从目前的结果看,这路电源的负载波动引起12V不干净,继而再干扰其他地方,导致系统fail,但目前没有实际证据证明这个推论,因为示波器测得的12V AC DC没发现异常,最关键的还是没找到什么信号被干扰,只找到干扰源,从暂时结果看,只能猜测干扰途径是该路电源input

你用纯电阻或者电子负载来作为53319的负载,看看是否还有1Hz信号,判定下是不是负载问题

非常感觉TI的各位FAE给予的热心帮助!

这个问题基本可以关闭了,从结果看,昨天的方向是对的,猜测结果与实验实际结果吻合,这个1Hz信号是负载引起的,很早以前就验证过这路53319外接电子负载看该路电源是否稳定。

这个问题总结如下:

这路电源负载电流变化比较大,周期性从几十mA跳变到6A左右,负载端夹杂的谐波也很多。负载的变化从而影响了这路电源输入端电源质量,输入端电源同时也给其他电源模块供电。

所以从干扰的特性来看,干扰源是这路电源负载的变化引起,传播途径是这路电源的输入,被干扰对象没有细分析(估计是同输入的某路敏感电压)。之前调试都是基于减小干扰源的基础上,有改善,但无法解决,目前的做法是切断干扰传播途径,输入端割线串磁珠,从而解决该问题。

1HZ的干扰也能用磁珠滤掉?

不能滤掉,1Hz是这路电源负载的固有特性,干扰源并不是这1Hz信号,而是周期性与非周期性负载变化产生的谐波引起,然后这路电源输入端PCB布局有个地方不是很好,从而通过输入端干扰到其他地方。

嗯嗯,建议你们参考数据手册或者WEBENCH进行合理布局,要用四层板为佳。

如果觉得问题解决,请帮忙将其close。选一个推荐答案,谢谢