关于UCC29950控制器PFC部分的逻辑问题,有没有TI的工程师可以帮助一下

我的逻辑为什么会和实际的结果恰恰相反,现在的纠结主要卡在PFC部分电流环的逻辑思路上,不知道是它逻辑图的问题还是我的思路问题,原理没搞透也不想盲目去把板子焊出来。

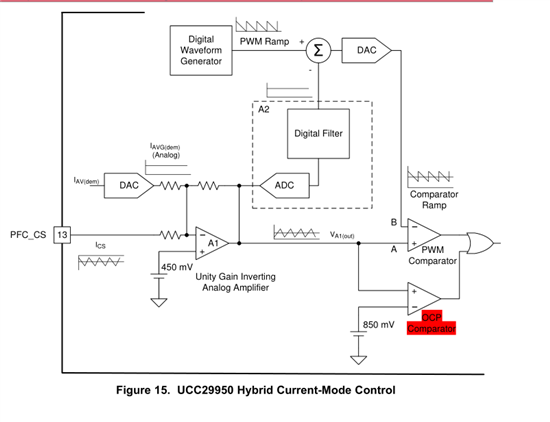

我的逻辑思路: PFC_CS电流反馈是负值输入,电压环的输出值用作电流环参考值Iav,然后跟采样回来的电感电流值(负)经过单位反向加法器处理,输出值一路被采样处理用作三角波的负增益,处理后的三角波作为PWM比较器的负输入端,另一路作为PWM比较器的正输入,两路比较之后产生PWM占空比。 所以,Iav增大,反向运放输出减小,PWM比较器负端输入增大,正端输入减小,PWM占空比是减小的,但实际占空比显然应该是增大的…

希望有人帮忙指点迷惑 或者讨论下 非常感谢

Hi

你描述的症结在于PWM比较器的逻辑输出。当Iav增加时,反向运放输出是变小,这个量与Ramp切出来的占空比是当VA〉VB时PWM比较器输出高,还是VA<VB输出高,我觉得是后者。如果是这样的话,就是Va1out输出减小,占空比增大。(三角波与直线切,中间部分是占空比输出,而非两边)

手册上是这样解释的:

If the I AV(dem) signal increases, for example in response to an AC line voltage or load change then the average

output of the A1 amplifier initially decreases by the same amount. The PWM duty cycle, and inductor current, will

then increase because as V A1(out) moves negative, it takes longer for the two signals at the comparator inputs to

intersect and terminate the cycle. The digital-filter output also increases in response to the change in V A1(out)

according to its frequency response characteristic and the average value of the comparator ramp moves

negative. This tends to reduce the PWM duty cycle. Eventually, as the PFC inductor current increases the V A1(out)

signal returns to its equilibrium point at 450 mV. The digital filter dynamically adjusts its output up or down so as

to keep the average value of the comparator ramp at the level where V A1(out) is kept at 450 mV. The overall effect

is that a unipolar sinusoidal demand signal is translated into a unipolar sinusoidal PFC inductor current.

我的理解力太差 搞的自己思维混乱了 可能也是初次接触这个东西