LM5085 FB管脚电压问题

接入负载后,设定负载电流为0.8A。发现FB管脚电压随输入电压13V-22V变化,从1.25V增长到1.34V。

这是什么原因?有什么解决办法么?

在FB引脚的电压发生变化时,电源的输出电压是否依然稳定?

Hi

关于电路,建议你参照webench仿真,包括器件的规格都是要注意的。

用示波器测试,你或可以看到输出存在不稳定,这个不稳定或许是Layout造成的。

电源输出电压发生变化。FB管脚的电压是由什么决定的?

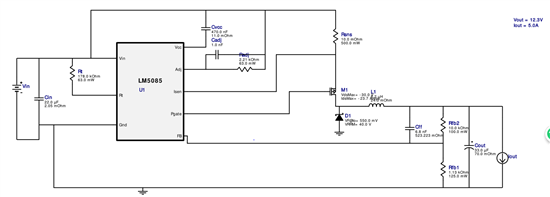

你好,FB电压是由输出电压经过电阻分压得到的,你可以把电路图发上来看一下。

另外附上生成的设计,唯一的区别是Cff 采用的是10nF

如附件,唯一的区别是Cff 采用10nF

如图,唯一的区别是Cff 采用10nF

发不上去。。。。。

按照仿真了啊。

Hi

前馈电容不能用得太大,可以看一下datasheet的描述。

Hi,

我也觉得是前馈电容的问题,一般这个电容取几十pF。这个前馈电容是为了改善环路响应特性的。您可以先试一下去掉前馈电容,看FB电压是否正常。再换上几十pF的试一下。 谢谢!

一般是取几十pF么?因为WEBENCH给的是6.8nF,刚才换成6.8nF,发现没有变化。

另外发现不加负载的情况下是1.25V,正常的。和负载有什么关系么?

不同的输入电压会对这个值有不同影响,会不会影响输出?

Hi,

抱歉刚没仔细看。查了一下手册,还是请按前面同事给出的那个公式来计算。

这个芯片内部不是误差放大器,而是比较器。可以请您贴出来加负载、不加负载FB pin上的波形吗?

没用示波器看波形。用万用表测电压就不对啊。加0.8A负载电流后,输入电压14V时输出正常为12.3V,FB管脚电压也是1.25V;但是输入电压增大到22V时,输出电压就上升到了13.5V,此时FB管脚电压是1.33V。

补充一下,负载用的是N3300A 直流电子负载。

Hi,

会不会是因为Layout的原因造成的,Feedback走线要远离开关节点。可以断开现有的FB走线,飞一根线试一下。

怎么飞线?另外输入和输出电容设计的偏大(输入时两个22uF并联,输出47uF)会有影响么?

很奇怪FB为什么会在有负载时随输入电压增大而增大,但没有负载时却不会。

你好,CFF容值建议改小试一下。

这颗芯片采用COT控制,通过比较器控制输出电压的纹波最低值。

输入电压越大,纹波越大,因此输出平均电压会随输入电压增大而略微增大。

已经改小到了3.3nF,还是不行。22V输入的时候还是13.4V左右。。有什么办法能让他在14V到22V输入之间都保持12.3V左右的输出么?另,无负载时14V到22V输入的输出也有增加。

hi,

请用pF级的前馈电容,于环路响应有关,也就与负载相关了,负载不同情况下响应不同

前馈电容按之前的datasheet里的公式算出来是nF级啊。。包括用webench仿真的也是nF级。。具体用多少比较好?

也就是说负载的变化也会影响输出电压?不同的负载,输出电压怎么算啊?没找到相应的公式?

前馈电容一般不大,输出负载影响环路稳定性,如果前馈电容不合适,是会影响的。计算公式是需要经过小信号建模得来。

那前馈电容怎么算呢?按公式和仿真的话是4-6nF啊?

请问,公式和仿真是按满载来的吗?尝试减小到几十pF时候是否还会有这样的问题?

Hi,

我觉得这个电容还是应该按照公式计算结果确定。首先这个芯片是类似于COT控制模式的,也就是恒定导通时间(但实际上根据手册来看,这个导通时间是根据Vin和Vout动态调整的,算是Adaptive on time吧)。这种控制模式并没有采用误差放大器,而是采用了误差比较器。误差比较器监测输出电压的值,一旦输出电压低于Vref,就打开上管导通一次。也就是说,实际的输出电压等于(Vref+1/2 Vripple)。纹波与Vin有关,Vin越高纹波越大,所以输出电压会随着Vin变化而有细小变化。

由于使用了误差比较器,要稳定工作则需要输出有一定的电压纹波。这个前馈电容的作用可以理解为,RC并联再与下位反馈电阻相连,减小了对于开关频率的纹波的阻抗,这样会“增强”FB引脚上的纹波信号。这也就是为什么,按手册上的计算公式,这个电容的取值与开关频率或者说是最大导通时间有关(3倍的关系)。综上我认为这个电容不能取太小。pF级一般是针对于误差放大器这种应用,环路补偿中为了改善稳定裕度所采用的。我最开始的时候也没有仔细看这个part,也以为应该取pf级,后来发现不是这样。

Hi,

关于输出的问题,我在想会不会是Layout的问题,FB走线应该远离SW节点。如果距离过近,SW节点的噪声耦合引入FB走线,也会导致输出电压变化。尤其这个芯片还是非同步的,续流二极管所在支路也应该远离。之前说FB飞线,就是如果PCB layout上FB走线没有远离开关节点,可以把FB线断掉然后单独焊一根飞线,让这条线远离开关节点,看输出是否还正常。

如您描述的现象,负载电流会影响到输出电压,我觉得有可能是因为FB线距离二极管所在支路较近,负载越大二极管所在支路电流突变越大,耦合过来的噪声就越大。您可以查看一下Layout看看是不是。所以还是建议您用示波器看一下SW, Vout和FB上的电压波形,贴出来一起分析。

谢谢!