关于tps63070在输入电压高时输出电压不正常的问题

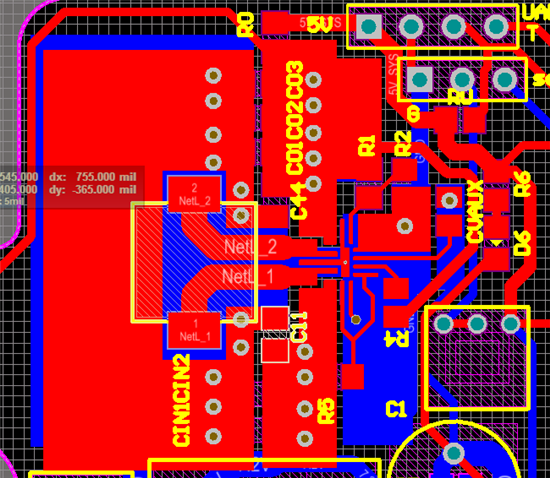

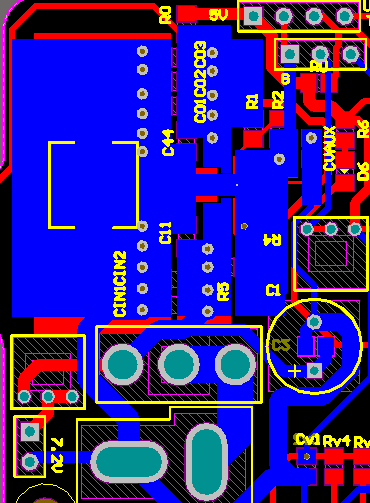

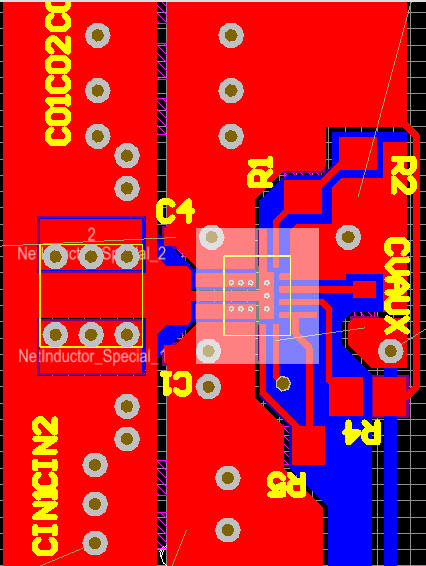

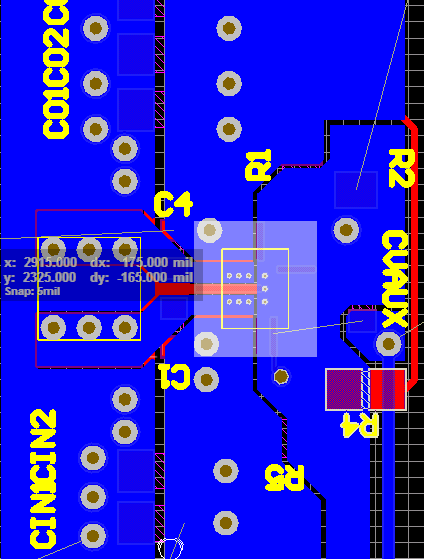

这是我对该模块的布局,现在出现了输入电压高时输出电压不正常的现象。具体为,tps63070和tps630701的板子在输入电压11V的时候输出只有2V多,tps63070的板子在输入电压降低至10.1V时回复正常,tps630701的板子在输入电压降低至9.2V,9.3V时回复正常,电路均按照5V的设计方法分别进行了两款不同元件的模块的焊接。这是怎么回事呢?

这是我对该模块的布局,现在出现了输入电压高时输出电压不正常的现象。具体为,tps63070和tps630701的板子在输入电压11V的时候输出只有2V多,tps63070的板子在输入电压降低至10.1V时回复正常,tps630701的板子在输入电压降低至9.2V,9.3V时回复正常,电路均按照5V的设计方法分别进行了两款不同元件的模块的焊接。这是怎么回事呢?

方便上传一下TPS63070 的L1 管脚波形么? 你的负载条件是什么? 5Vout,输入电压范围多少?

还有TPS630701 这个料号貌似不对吧

你好,将PS/SYNC 管脚接地,再看一下工作是否正常.

Hi

对于处在降压中的芯片,输入电压越高,电路峰值电流越高,对于layout要求也就越高。

如果电感饱和电流没有问题,你需要注意layout(datasheet上有参考,你的layout看起来不是太好),主要注意功率路径尽量小,避免寄生参数,

不行,电路设计时PS/SYNC 管脚和EN管脚连在一起了,给低电平就不工作了。

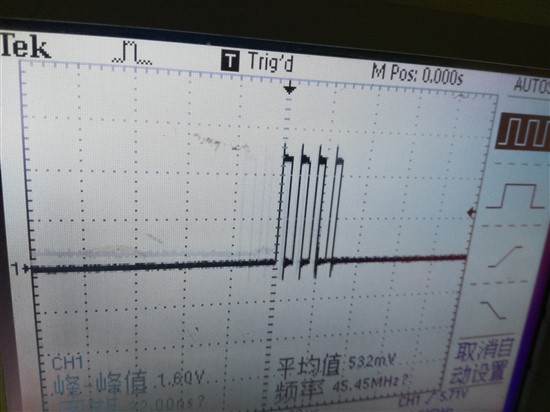

12V的时候,输出电压5.6,高于所需要的5V很多。照片如下

这个波形很难拍到而且时有时无。然后是11V左右输入时输出3V多一点,波形是这样的

这个波形很难拍到而且时有时无。然后是11V左右输入时输出3V多一点,波形是这样的

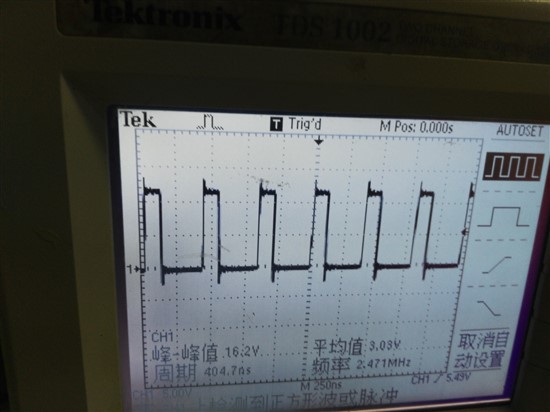

然后是输入10.5V左右时候,就输出5V了

然后是输入10.5V左右时候,就输出5V了

1,在不正常工作时,PG管脚波形如何

2,我看你的第一张图片有点像PSM,你将铜皮割断,把PS连接到地试一下

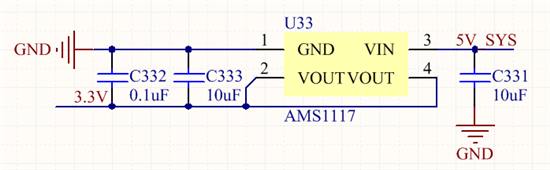

因为马上要用了,再设计一版已经来不及了,现在就希望在合理的范围内简单改一改元件取值,必要的时候飞一下线,能在12V以下都正常工作,还不会损坏这个芯片就行了,也不需要像技术手册里那样输入电压16V。我后续用了AMS1117,上面输入端也接了不少电容,在想是不是TPS63070输出侧电容过大也有影响。现在那里用了三个22uf的电容,后续AMS1117 5V转3.3V模块原理图如下。

或者说更改电感取值之类的。

你好,输出电容过大的确会影响环路,但是你的输出电容为22×3+10uF,对电路环路影响应该不大。

电路中选取的电感是功率电感么?

电感是功率电感。除此之外输出端按照datasheet的原理图还有一个10uf也并在那两端,以及可能还有几个电容分布在其他模块(单片机和其他硬件配合的接口,有在他们上也并了几个小的)上没有写出来,不过小模块用的也就是0.1uf的这种。

建议先不要接AMS1117,带纯阻性负载,观察是否 还有这样的现象

你的电感得换一个铁氧体电感,具体型号可以参考数据手册

行,我明天去买一个试试。感谢您的回复。

您好,我还想问您一下,除了以上更改以外,更换功率电感取值对于这个问题有没有改善?

你的电感适合的工作频率在MHz以内,而你的芯片频率在2.4MHz, 在这么高的频率下,电感衰减(感值,饱和电流,有效值)的很多, 所以很有可能导致上述现象。

另外 坦白的说,这个芯片外围器件就这么几个,不应该出现你这样的情况,一般的问题就是取值不对,或者layout不好。你的layout虽然不是最好,但是不应该会有那么大的影响以至于高输入时出不了电压。现在的方法就只能逐一排查。

等于说我应该提高一下电感值试试,也许会好一点?

不是提升电感值,是需要更换成功率铁氧体电感。

因为在高频下,你现在用的电感不知道会衰减到什么程度,而且其他的一些磁场问题也无法估计,所以需要把它更换

好,我明白了,感谢您的回复。

您好,我最后想在改善layout等方面问您一些问题。电感L的布线是不是从板子两面过都可以,也就是电感的线从背面过,然后在焊盘上加个过孔这样?其余电路部分有没有距离限制,比如说要给电源模块这里留开足够的空间,电源模块内部的某些元件或某些走线要远离某类信号线或者电源线之类的? 我使用的电源是超级电容有没有什么大的影响,需不需要有特别要注意的?更换了铁氧体电感之后,还是没能达到自己理想中的效果,大概大于10.5V输入就不能正常工作了,之前一段时间够用了,不过还是希望能改善到带负载以后12V以上也可以用,这是我心里比较理想的状况。

电感的布线可以在底层,然后通过过孔实现,但节点的铜皮面积不要太大,容易引起EMI问题。

其次输入电容,还有反馈电阻尽可能的靠近芯片,但小信号部分最好和大信号离得远一点,避免串扰。

建议你要使用稳压源测试,验证芯片工作是否正常,再去使用超级电容试验。

节点的铜皮面积不要太大是什么意思呢?是电感的焊盘么?

顺便问您一个基本的问题吧,这个问题查了很久没弄明白。

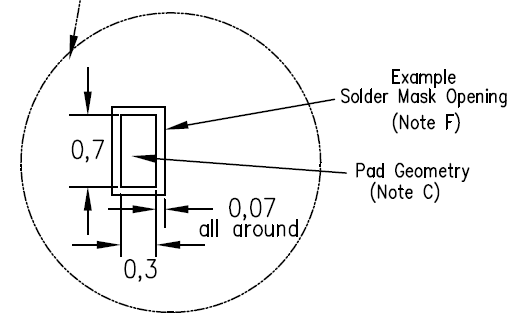

。如果用altium designer画PCB封装,像是这张图里面的solder mask和pad分别对应的是哪一层的?我在网上查到阻焊层是用于焊接的,那为什么要标一个单独的焊盘的大小呢?

。如果用altium designer画PCB封装,像是这张图里面的solder mask和pad分别对应的是哪一层的?我在网上查到阻焊层是用于焊接的,那为什么要标一个单独的焊盘的大小呢?

节点指的是电感和开关管的连接处,就是芯片引脚和电感焊盘连接的铜皮,但其不能太细,面积也不宜过大

对于焊盘,AltiumDesign里面会有专门的Bottom/Top solder(阻焊层),还有Top/Bottom paste(助焊层),

阻焊层中画的部分会取消阻焊剂使PCB板可以挂锡,助焊层叫锡膏层,用来涂抹锡膏。

Solder mask 就是阻焊层,里面的可以是助焊层,也可以是铜皮,看你在软件里怎么设计了

也就是说是要把走线布的短粗一点的意思是么?您说的有点深我不是很明白。以我能理解的范围,芯片引脚和电感焊盘之间只有芯片焊盘和走线了。如果不是优化走线的话,那就是弄小芯片焊盘了?我为了方便焊接在画封装的时候把芯片的各个焊盘画得比技术文档里的长了一点,是指这一部分应该弄小一点么。

对了,我使用了0805的电感C1、C4和CVAUX,这个影响会不会很大。我看技术手册上推荐的前两个是0603,后一个是0402的,这个换了会不会有影响,之前是因为方便所以才用了0805的。0603的我倒是好弄,0402的似乎不太好弄,封装和元件都没有现成的,如果可以的话CVAUX用0603的可不可以,会不会比0805好一些?

焊盘大一点点没关系,我说的节点面积主要还是电感和芯片的连线,要短粗。

元器件尺寸没有关系,只要耐压和温度特性指标(X5R或X7R)选对就可以

您好,我还想问您一个问题。我重新设计了一下板子,但是有一块我不太拿得准主意。

第二张图芯片中心处的GND要不要和左边的敷铜连起来。我怕连起来之后GND会形成一个环,又离电感近,造成干扰。但是不连起来我又怕只有正面该处GND把左右连在一起走线会烧掉(正面焊盘宽13mil多一点)。我如果不把右边的GND连到外电路使用,而是单独在那里,会烧掉么?GND我从电源处单独引一个出来

第二张图芯片中心处的GND要不要和左边的敷铜连起来。我怕连起来之后GND会形成一个环,又离电感近,造成干扰。但是不连起来我又怕只有正面该处GND把左右连在一起走线会烧掉(正面焊盘宽13mil多一点)。我如果不把右边的GND连到外电路使用,而是单独在那里,会烧掉么?GND我从电源处单独引一个出来

我不太明白你的意思,不过你可以参考以下文件进行版图设计

http://www.ti.com/lit/ug/slvuao5/slvuao5.pdf

这个模块的右边那里的GND只有第一张图toplayer中间那个焊盘那里连到左边再连到电源,其他路径没有连到电源,因而如果右边那里GND部分电流很大,中间那个焊盘又很小,就会烧掉中间那一段很细的走线。我是担心出现这种情况。

不过您给我的文档中没有连起来,看来是电流不足以烧毁中间那一小段走线。